# SYRCoSE 2014

# Editors:

## Alexander Kamkin, Alexander Petrenko and Andrey Terekhov

Preliminary Proceedings of the 8<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering

Saint Petersburg, May 29-31, 2014

#### Preliminary Proceedings of the 8<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE 2014), May 29-31, 2014 – Saint Petersburg, Russia:

The issue contains the papers presented at the 8<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE 2014) held in Saint Petersburg, Russia on May 29-31, 2014. Paper selection was based on a competitive peer review process being done by the program committee. Both regular and research-in-progress papers were considered acceptable for the colloquium.

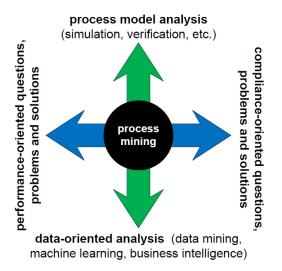

The topics of the colloquium include formal methods, embedded system design, system programming, process mining, testing, compiler technologies and others.

Предварительный сборник трудов 8-ого весеннего/летнего коллоквиума молодых исследователей в области программной инженерии (SYRCoSE 2014), 29-31 мая 2014 г. – Санкт Петербург, Россия:

Сборник содержит статьи, представленные на 8-ом весеннем/летнем коллоквиуме молодых исследователей в области программной инженерии (SYRCoSE 2014), прошедшем в Санкт Петербурге 29-31 мая 2014 г. Отбор статей производился на основе рецензирования материалов программным комитетом. На коллоквиум допускались как полные статьи, так и краткие сообщения, описывающие текущие исследования.

Программа коллоквиума охватывает следующие темы: формальные методы, проектирование встроенных систем, системное программирование, анализ процессов, тестирование, компиляторные технологии и др.

ISBN 978-5-91474-020-4

## Contents

| Foreword5                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Committees / Referees                                                                                                                  |

| Formal Methods                                                                                                                         |

| Modular Construction of Time Petri Nets Reachability Graph<br>I. Knizhnikova, L. Dworzanski                                            |

| On the Deadlock Control in Parallel Resource-Constrained Workflows<br>V. Bashkin, N. Panfilova                                         |

| LTL-Specification, Verification and Construction of PLC Programs<br>D. Ryabukhin, E. Kuzmin 19                                         |

| An Approach to Lightweight Static Data Race Detection<br>P. Andrianov, A. Khoroshilov, V. Mutilin27                                    |

| Minimizing the Number of Static Verifier Traces to Reduce Time for Finding Bugs in Linux Kernel<br>Modules<br>V. Mordan, E. Novikov    |

| Tools Support for Linux Kernel Deductive Verification Workflow<br>D. Efremov, N. Komarov40                                             |

| Dynamically Allocated Memory Verification in Object-Oriented Programs using Prolog<br><i>R. Haberland, S. Ivanovskiy</i>               |

| Embedded System Design and System Programming                                                                                          |

| Energy-Aware Design of Embedded Software through Modelling and Simulation<br>J.A. Esparza Isasa, P.G. Larsen, F.O. Hansen              |

| Energy Aware Congestion Management in Dynamic Wireless Mesh Network<br>S.P. Shiva Prakash, T.N. Nagabhushan, K. Krinkin, O. Sholokhova |

| An Architecture of Effective Discrete-Event Simulation Engine for Early Validation of Avionics Systems<br>D. Buzdalov                  |

| Protecting Applications from Highly Privileged Malware Using Bare-metal Hypervisor<br><i>K. Mallachiev, N. Pakulin</i>                 |

| Process Mining                                                                                                                         |

| Checking Conformance of High-Level Business Process Models to Event Logs<br>A. Begicheva, I. Lomazova                                  |

| Applying Graph Grammars for the Generation of Process Models and Their Logs<br>V. Kataeva, A. Kalenkova······83                        |

| Generation of a Set of Event Logs with Noise<br><i>I. Shugurov, A. Mitsyuk</i> ······88                                                |

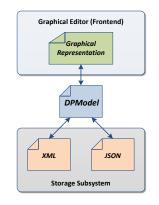

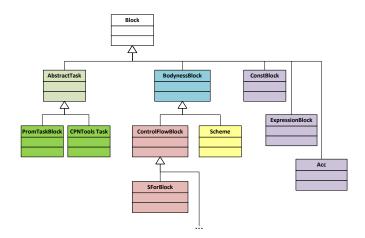

| DPMine/C: C++ Library and Graphical Frontend for DPMine Workflow Language<br>S. Shershakov                                             |

| Component-based VTMine/C Framework: Not Only Modelling<br>P. Kim, O. Bulanov, S. Shershakov                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Testing                                                                                                                                              |

| Extended Finite State Machine based Test Derivation Strategies for Telecommunication Protocols<br>N. Kushik, A. Kolomeez, A. Cavalli, N. Yevtushenko |

| A Generic Knowledgebase for Test Generation<br>A. Kotsynyak, A. Tatarnikov                                                                           |

| Interactive Test Case Design via Attribute Exploration<br>F. Strok, G. Kondratiev 118                                                                |

| Keyword-Driven Testing with Message Sequence Charts<br>B. Tyutin, A. Veselov, V. Kotlyarov                                                           |

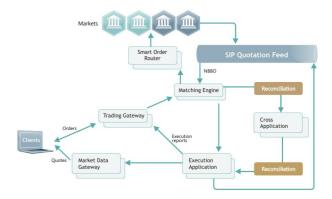

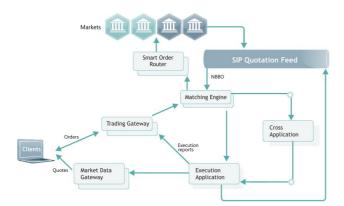

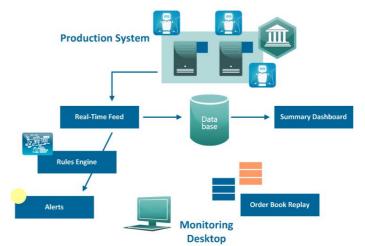

| Reconciliation Testing Aspects of Trading Systems Software Failures<br>AM. Kriger, V. Isayev, A. Pochukalina                                         |

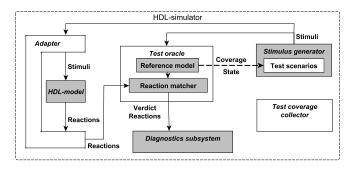

| Simulation-based Hardware Verification Back-end: Diagnostics<br>M. Chupilko, A. Protsenko                                                            |

| Compiler Technologies                                                                                                                                |

| From Abstract Parsing to Abstract Translation<br>S. Grigoriev, Ia. Kirilenko                                                                         |

| Comparison of Generalized Ascent and Descent Parsers<br>A. Ragozina, S. Grigoriev                                                                    |

| One Approach to Automated Compiler Verification<br>V. Bessonov, L. Lyadova                                                                           |

| Generation of Overlapped Executable Code<br>V. Aranov, A. Terentiev                                                                                  |

| Application-Specific Methods and Tools                                                                                                               |

| Predicative Analytics for Developing Software<br>N. Yarushkina, T. Afanasieva, I. Timina                                                             |

| Detecting and Highlighting Text in Images<br><i>I. Pakhomov</i>                                                                                      |

| Using Multidimensional Ontology of Electronic Document for Solving Semantic Indexing Problem<br>V. Lanin, G. Sokolov                                 |

| Generation of Domain-Specific Languages on the Basis of Ontologies<br>A. Sukhov                                                                      |

| Dynamic Information Model Interactions: Design and Implementation of Database-Driven Workflow<br>Approach<br><i>A. Petrov</i>                        |

## Foreword

Dear participants, we are glad to meet you at the 8<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE). The event is held in Saint Petersburg, the second largest city in Russia and its cultural capital. The colloquium is hosted by Saint Petersburg State Polytechnical University (SPbSPU), one of the top research and educational institutions in Russian Federation in the field of applied physics and mathematics, industrial engineering, chemical engineering, aerospace engineering and many other disciplines. SYRCoSE 2014 is organized by Institute for System Programming of the Russian Academy of Sciences (ISPRAS) and Saint Petersburg State University (SPbSU) jointly with SPbSPU.

In this year, Program Committee (consisting of 50 members from more than 25 organizations) has selected 31 papers. Each submitted paper has been reviewed independently by three referees. Participants of SYRCoSE 2014 represent well-known universities, research institutes and companies such as Aarhus University, Exactpro Systems, ISPRAS, JSS Research Foundation, JSS Academy of Technical Education, Kostroma State Technological University, National Research University – Higher School of Economics, Obninsk Institute for Nuclear Power Engineering, Perm State National Research University, Saint Petersburg Electrotechnical University "LETI", SPbSPU, SPbSU, TELECOM SudParis, Tomsk State University, Ulyanovsk State Technical University, Yandex, Yaroslavl State University and Yuri Gagarin State Technical University of Saratov (4 countries, 13 cities and 18 organizations).

We would like to thank all of the participants of SYRCoSE 2014 and their advisors for interesting papers. We are also very grateful to the PC members and the external referees for their hard work on reviewing the papers and selecting the program. Our thanks go to the invited speakers, Bertrand Meyer (ETH Zürich, Switzerland) and Kostya Serebryany (Google Moscow, Russia). We would also like to thank our sponsors and supporters: Russian Foundation for Basic Research (grant 14-07-06006), Google, Exactpro Systems and CyberLeninka. Finally, our special thanks to local organizers, Igor Chernorutskiy, Vsevolod Kotlyarov and Tatyana Elamic (SPbSPU), for their invaluable help in organizing the colloquium in Saint Petersburg.

Sincerely yours

Alexander Kamkin, Alexander Petrenko and Andrey Terekhov May 2014

## Committees

### **Program Committee Chairs**

Alexander Petrenko – Russia Institute for System Programming of RAS

### **Program Committee**

Jean-Michel Adam – France Tiziana Margaria – Germany Pierre Mendès France University University of Potsdam Sergey Avdoshin - Russia Marek Miłosz - Poland National Research University Higher School of Economics Institute of Computer Science, Lublin University of Technology Eduard Babkin - Russia Alexey Namestnikov - Russia National Research University Higher School of Economics Ulyanovsk State Technical University Svetlana Chuprina – Russia Valery Nepomniaschy – Russia Perm State National Research University Ershov Institute of Informatics Systems Pavel Drobintsev - Russia Mykola Nikitchenko – Ukraine Saint-Petersburg State Polytechnic University Kyiv National Taras Shevchenko University Liliya Emaletdinova – Russia Yuri Okulovsky – Russia Institute for Technical Cybernetics and Informatics, KNRTU Ural Federal University Elena Pavlova - Russia Victor Gergel - Russia Lobachevsky State University of Nizhny Novgorod Microsoft Research Efim Grinkrug – Russia Ivan Piletski – Belorussia Belarusian State University of Informatics and Radioelectronics National Research University Higher School of Economics Maxim Gromov – Russia Vladimir Popov – Russia Tomsk State University Ural Federal University Vladimir Hahanov – Ukraine Yury Rogozov – Russia Kharkov National University of Radioelectronics Taganrog Institute of Technology, Southern Federal University Rustam Sabitov - Russia Shihong Huang – USA Florida Atlantic University Kazan National Research Technical University Iosif Itkin - Russia Nikolay Shilov - Russia Ershov Institute of Informatics Systems Exactpro Systems Alexander Kamkin – Russia Ruslan Smelyansky - Russia Institute for System Programming of RAS Moscow State University Vsevolod Kotlyarov - Russia Valeriy Sokolov – Russia Saint-Petersburg State Polytechnic University Yaroslavl Demidov State University Oleg Kozyrev – Russia Petr Sosnin – Russia National Research University Higher School of Economics Ulyanovsk State Technical University Vladimir Kozyrev – Russia Veniamin Tarasov – Russia Povolzhskiy State University of Telecommunications and Informatics National Research Nuclear University "MEPhl" Daniel Kurushin – Russia Sergey Ustinov - Russia Saint-Petersburg State Polytechnic University State National Research Polytechnic University of Perm Peter Gorm Larsen – Denmark Vladimir Voevodin – Russia + Research Computing Center of Moscow State University Aarhus University Dmitry Volkanov - Russia Rustam Latypov – Russia Institute of Computer Science and Information Technologies, KFU Moscow State University Alexander Letichevsky – Ukraine Mikhail Volkov – Russia Glushkov Institute of Cybernetics, NAS Ural Federal University Alexander Lipanov – Ukraine Nadezhda Yarushkina – Russia Kharkov National University of Radioelectronics Ulyanovsk State Technical University Irina Lomazova - Russia Rostislav Yavorsky - Russia National Research University Higher School of Economics National Research University Higher School of Economics Ludmila Lyadova – Russia Nina Yevtushenko – Russia National Research University Higher School of Economics Tomsk State University Victor Malyshko - Russia Vladimir Zakharov - Russia Moscow State University Moscow State University Vladimir Makarov – Russia Sergey Zaydullin – Russia Yaroslav-the-Wise Novgorod State University Kazan National Research Technical University

### **Organizing Committee Chairs and Secretaries**

Alexander Petrenko – Russia Institute for System Programming of RAS Vsevolod Kotlyarov – Russia Saint-Petersburg State Polytechnic University

Andrey Terekhov – Russia

Saint-Petersburg State University

## Referees

Jean-Michel Adam Sergey Avdoshin **Eduard Babkin** Mikhail Chupilko Svetlana Chuprina Pavel Drobintsev **Denis** Efremov Victor Gergel Efim Grinkrug Maxim Gromov Shihong Huang Iosif Itkin **Dmitry Ivankov** Anna Kalenkova Alexander Kamkin Dmitry Kosolobov Vsevolod Kotlyarov Artem Kotsynyak Vladimir Kozyrev Daniel Kurushin Peter Gorm Larsen Alexander Lipanov Irina Lomazova Lyudmila Lyadova Victor Malyshko

Tiziana Margaria Ivan Mikhailov Alexey Namestnikov Mykola Nikitchenko Yuri Okulovsky Nikolay Pakulin Elena Pavlova Alexander Petrenko Ivan Piletski Vladimir Popov Yury Rogozov Nikolay Shilov Sergey Smolov Valeriy Sokolov Petr Sosnin Veniamin Tarasov Andrei Tatarnikov Andrey Terekhov Dmitry Volkanov Mikhail Volkov Nadezhda Yarushkina Rostislav Yavorskiy Nina Yevtushenko Vladimir Zakharov

# Modular construction of Time Petri net reachability graph

Ilona Knizhnikova National Research University Higher School of Economics iknizhnikova@gmail.com

Abstract—Time Petri nets are an extension of Petri nets formalism with time specifications on transitions. The formalism is convenient to model distributed systems and enables capturing the time characteristics of distributed system activities. The primary tool for models behaviour understanding is reachability graph. In [10] the algorithm for constructing Time Petri net reachability graph was suggested. It is based on *essential* states, but the number of states in the resultant net reachability graph increases when time specification are scaled up, while the behaviour of the net is invariant under time specification scaling. We study the modification of this algorithm that allows to build Time Petri nets reachability graphs more efficiently using common divisors of the time specification in the components of a Time Petri net.

Keywords—time petri nets, reachability graph, essential states.

#### I. INTRODUCTION

Petri nets are a popular formalism for modelling concurrent systems. Different extensions of Petri nets and their applications are extensively studied in the literature [12], [3], [2], [11], [4], [6]. Obviously, time is the very important aspect of systems behaviour. Time restrictions like "this action can take from N to M seconds" are crucial for real-time system, net protocols, control systems et cetera. Time can be introduced into the Petri nets formalism in many different ways [1]. Moreover, even timeless distributed systems are hard to understand [8], [5]. There are two popular types of such nets: time Petri nets and timed Petri nets. Both of these modifications can simulate counter machines, i.e. are Turing-complete. Both can be used to model systems with time specifications, but in this article only time Petri nets are considered.

Time restrictions make behaviour of Time Petri nets models extremely hard to understand. It means that we have no options but to use computer aided means to check the correctness of a developing system or to analyze already constructed one. The crucial tool to understand the behaviour of a model is reachability graph. The problem of time Petri nets model checking can be solved via essential-states-based algorithm for constructing reduced reachability graphs [9]. But when all time specifications of a Time Petri net are multiplied by a constant, the size of reachability graph is increased or decreased while the behaviour of the net has not changed. In this work we study how to use this property of the algorithm to reduce the space requirements for analysis of a Time Petri net.

The paper is organized as follows. To start with, we provide basic notations of Petri nets. Then we define the Time Petri nets formalism. Then we provide a Time Petri net example which captures the process of a university course from the student Leonid Dworzanski National Research University Higher School of Economics leo@mathtech.ru

viewpoint. After that we apply our modification to build the reachability graphs of the net components of the example and provide the obtained results. The paper ends with conclusion.

#### II. PRELIMINARIES

Petri nets are a well known formalism widely used to model concurrent systems. Petri nets offer graphical notation and rigorous formal semantics. A Petri net is a marked directed bipartite graph, where the structure of the graph defines the behaviour of the model while the marking of the graph defines the current state.

Definition 2.1: A Petri (P/T-net) net is a 4-tuple (P,T,F,W) where

- P and T are disjoint finite sets of places and transitions, respectively;

- $F \subseteq (P \times T) \cup (T \times P)$  is a set of arcs;

- W: F → N an arc multiplicity function, that is a function which assigns every arc a positive integer number (arc multiplicity).

Following extension of W we denote as W:

$$\widetilde{W}(x,y) = \left\{ \begin{array}{ll} n, & xFy \wedge W(x,y) = n \\ 0, & \neg xFy \end{array} \right.$$

A marking of a Petri net (P,T,F,W) is a multiset over P, i.e. a mapping  $M : P \to \mathbb{N}$ . By  $\mathcal{M}(N)$  we denote a set of all markings of a P/T-net N. We say that the transition t in a P/T-net N = (P,T,F,W) is active in the marking M iff for every  $p \in \{p | (p,t) \in F\} : M(p) \ge \widetilde{W}(p,t)$ . An active transition may fire, resulting in a marking M' such that  $\forall p \in P : M'(p) = M(p) - \widetilde{W}(p,t) + \widetilde{W}(t,p)$ .

Another notion we will use is hammock. While it is well known notion we will recall it informally. Hammock is a part of the graph such, that only two vertexes of hammock are linked with the rest of the graph. These vertexes are called starting and ending vertexes of hammock. There can be the subgraph of arbitrary complexity between these two vertexes, but this system should have no link to the graph except starting and/or ending vertex of hammock. [7]

#### III. MOTIVATING EXAMPLE

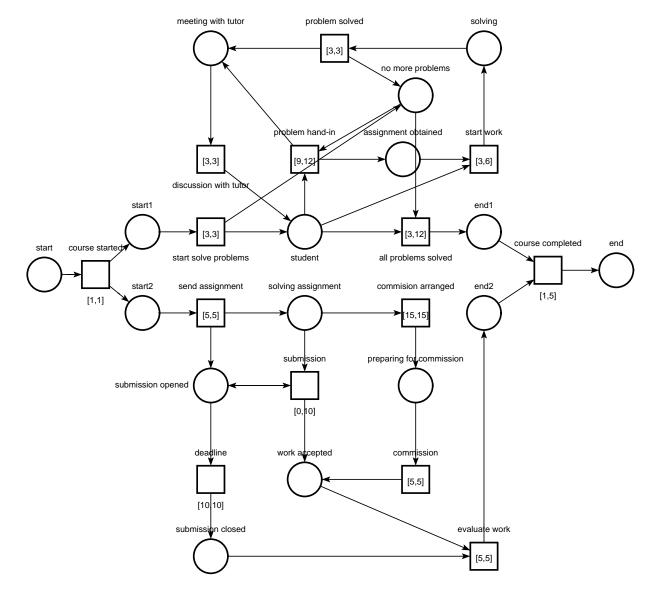

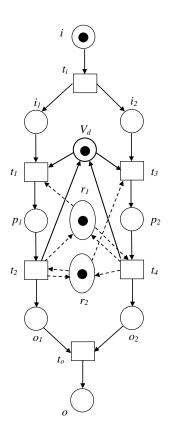

In this section, we provide the example of a time Petri net Tnet that models the flow of some course.

The first transition of the Tnet denotes the beginning of a semester and the beginning of a course. The process consists of two almost independent scenarios, each of whose is represented by a separate net hammock. First of them (starting with the place *start1* and ending with *end1*) can be interpreted as the process of preparing for exams and working with a teacher. Second one models an examination process. The course can be completed iff these parts are performed successfully, i.e. final mark depends on both of them. But they do not block each other — a student has to pass the exam without regard to his work during the semester.

The process starts with a transition *course started* firing, which adds tokens to the places *start1* and *start2*. Then two hammocks are performing independently.

We start with considering the upper hammock. Firstly, transition start solve problems fires. It represents the beginning of student's work and adds tokens to the places student and no more problems. When both of these places contain tokens student isn't solving a problem and is ready for actions. The course can be ended through firing the transition all problems solved, or the student can get some new problems to solve (transition hand-in problem). In the second case, the student needs to solve the problem. He or she starts with meeting with a tutor (going to place *meeting with tutor*), discusses the problem (transition discussion with tutor moves token to the place *student* and this enables transition *start work*) and then student starts working on it, and comes to some decision. (Transition start work fires and moves token to the place *solving*). After that, the problem is technically solved and transition problem solved fires adding token to the place no more problems, but the student still needs to meet his tutor again to discuss the result. (Chain meeting with tutordiscussion with tutor-adding token to place student fires again). Only after that student understands the nuances of the problem and the solution well enough.

Then the cycle may repeat again — student ends the process or gets a new problem. If the first case has place, the hammock finishes its execution.

Now we consider the second hammock. This hammock starts with transition *send assignment* firing adding tokens to places *solving assignment* and *submission opened*. Then the hypothetical student has two options: complete his work before deadline (transition *submission*), let the system register his work (transition *deadline*), and then just get his mark by getting through transition *evaluate work*.

If student had not managed to pass his work in time, the system registers this (transition *deadline*) and the submission is closed (disabling transition *submission*). Then he or she has no choice, but to pass the work behind time (transition *commission arranged*), wait for a re-examination (place *preparing for commission*) and go through it (transition *commission*). Independently of the success or the failure of his examination, the student gets his mark — would it be A or F at the transition *evaluate work* firing.

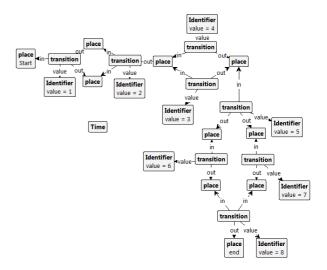

We will not provide the formal definition of a workflow net here, but this model is a sound workflow net, i.e. initial marking has one token in the *start* place. When a token reaches the *end* place there are no other tokens in the net. And the marking with the *end* place marked can always be reached.

#### IV. TIME PETRI NETS

In this section we define Time Petri nets (TPN).

We will use the definition of Time Petri net as given in [10]. Time Petri net (TPN) is an extended classic Petri net where each transition t is associated with a time interval  $[a_t, b_t]$ . If t is enabled, it still cannot fire before  $a_t$  time units have elapsed, and it has to fire no later than  $b_t$  time units after being enabled, unless it has meanwhile become disabled by the firing of another transition.

Time counting is started from the moment of enabling t and is reset if t has been disabled.  $a_t$  is called "earliest firing time" of t (short eft(t)) and  $b_t$  is "latest firing time" of t (short lft(t)). The firing of a transition does not take any time.

The interval bounds are non-negative rational numbers, and  $b_t$  can also be  $\infty$ .

Definition 4.1: A Time Petri net (TPN) is a 6-tuple  $Z = (P, T, F, V, m_0, I)$  such that

- 1) the 5-tuple  $S(Z) = (P, T, F, V, m_0)$  is a Petri net,

- 2)  $I:T\to Q_0^+\times (Q_0^+\cup\infty)$  and for each  $t\in T,$  with I(t)=(I1(t),I2(t)) it holds that  $I1(t)\leq I2(t)$

Here I(t) is the time interval of the transition t, during this interval t is ready to fire, I1(t) is eft(t) and I2(t) is lft(t).

Definition 4.2: (p-marking) Let P be the set of all places in a Time Petri net Z. A p-marking in Z is a (total) function  $m: P \to \mathbb{N}$ .

Definition 4.3: (t-marking) Let T be the set of all transitions in a time Petri net Z. Any (total) function  $h: T \to \mathbb{R}^+_0 \cup \#$ is a t-marking in Z.

Definition 4.4: Let  $Z = (P, T, F, V, m_o, I)$  be a Time Petri net, m a p-marking and h a t-marking in Z. A state in Z is a pair z := (m, h) such that

1)  $\forall t((t \in T \land t^- > m) \to h(t) = \#).$

2)

$$\forall t((t \in T \land t^- < m) \rightarrow h(t) \in \mathbb{R}^+_0 \land h(t) < lft(t)).$$

**Claim 1.***Time specification of transitions of an arbitrary time Petri net can be required to be non-negative integers without loss of generality [10]*

#### V. REACHABILITY GRAPH

Firstly we consider original algorithm proposed in [10]. It is based on the conception of essential states.

Definition 5.1: (modified state change) Let  $\tau$  be a nonnegative real number and z = (m, h) be a state in the Time Petri net Z. It is possible for time  $\tau$  to elapse in the state z in Z if

$$\forall (t \in T \land h(t) \neq \rightarrow h(t) + \tau \leq lft(t))$$

The elapsing of time  $\tau$  will change z into the state z' = (m', h') with

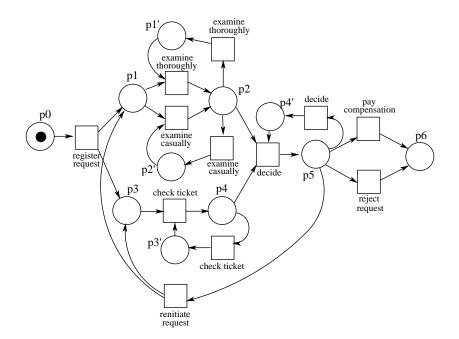

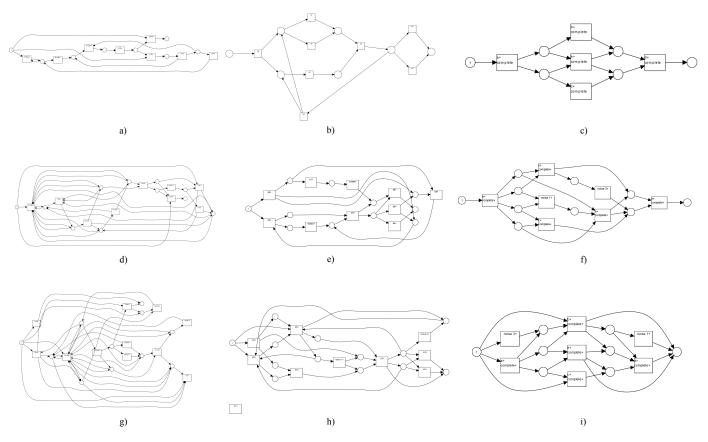

Fig. 1. The workflow net of a course process

2)  $\forall t \in T \rightarrow$

$$h'(t) := \left\{ \begin{array}{ll} \# & \text{if } ift^- > m' \\ eft(t) & t^- \leq m' \wedge lft(t) = \infty \\ & \wedge eft(t) < h(t) + \tau \\ h(t) + \tau & \text{otherwise} \end{array} \right.$$

*Definition 5.2:* (essential-state) An integer-state z = (m, h) in a Time Petri net Z is called essential-state when Z is defined with the modified firing rule.

*Definition 5.3:* (reachable essential-state) Let Z be an arbitrary Time Petri net. The set  $REIS_Z$  of all reachable essential-states in Z is defined as follows:

$REIS_Z := \{z | z_0 \xrightarrow{\sigma(\tau)} z\}, z \text{ is an essential-state and } \sigma(\tau)$  is a run feasible in Z

Set of all reachable essential states of the net carries complete information about this net's behavioural properties. This characteristic makes it possible to construct reachability graph, which includes only essential states (and is much smaller than original reachability graph) and still provides enough information to analyse behavioural properties of the net.

Definition 5.4: (reachability graph for arbitrary Time Petri net) Let  $Z = (P, T, F, V, m_0, I)$  be an arbitrary (finite or infinite) Time Petri net with  $T = t_1, \ldots, t_n$ . The (reduced) reachability graph  $RG_Z^{redu} := (W, E, L)$  of Z is the directed graph with edge labels whose set of vertices W, set of edges E and edge labels from  $L \subseteq N \times T$  are defined by Algorithm 1. Algorithm 1: Time Petri net reachability graph

$$\begin{array}{c|c} \textbf{begin} \\ R := Z_0; W := \emptyset; E := \emptyset; \\ \textbf{while } R \neq \emptyset) \textbf{ do} \\ & \textbf{select } z = (m, h) \text{ from } R; R := R - \{z\}; \\ W := W \cup \{z\}; \\ \textbf{ if } \{t \in T | t^- \leq m\} \neq \emptyset \textbf{ then} \\ & \textbf{ if } \{t \in T | t^- \leq m \land lft(t) \neq \infty\} \neq \emptyset \textbf{ then} \\ & \textbf{ let } k := min\{lft(t) - h(t)|t^- \leq m\} \\ & \textbf{ else} \\ & \textbf{ let } k := max\{eft(t) - h(t)|t^- \leq m\} \\ & \textbf{ for } i = 1 \textbf{ to } n \textbf{ do} \\ & \textbf{ for } i = 1 \textbf{ to } n \textbf{ do} \\ & \textbf{ lif } t_i \text{ ready to fire } in (m, h) + time \textbf{ then} \\ & \textbf{ Let } z' \text{ be such that } z \xrightarrow{time t_i} z'; \\ & E := E \cup \{(z, [time, t_i], z')\}; \\ & \textbf{ if } z' \notin W \textbf{ then} \\ & \textbf{ Let } R := R \cup \{z'\} \end{array}$$

#### VI. MODULAR CONSTRUCTION OF TIME PETRI NET REACHABILITY GRAPH

Algorithm constructing reachability graph through essential states demonstrates high performance, when it works with nets, whose time intervals are not very big. But if we multiply all time specifications in a net on the same number, number of essential states increases dramatically. But such scaling does not affect behavioural properties of the net and the set of reachable p-markings of the scaled and the original nets are the same.

There is an evident way to fix the problem — just check if the net can be down-scaled (divided by greatest common divisor) and than analyse this downscaled net. But what if we have the net consisting of two independent components. Both of these components can be down-scaled, if considered independently, but the time specification of these components contains coprime numbers.

Such net can have huge reachability graph, which can not be constructed because of the time or memory restrictions. But the graphs for each of these parts can easily be built via the downscale procedure. And these graphs carry enough information to analyse behavioural properties of the original net, such as boundedness, for example. We propose the way to solve the problem through searching for the detached hammocks, finding greatest common divisor (GCD) for all natural time specification inside them, dividing these specifications on the GCD and than applying reachability graph construction algorithm to each of the found hammocks.

Obtained reachability graphs can be used for performing model checking upon each of them and deduce identified properties for the whole net, but for the moment we consider only receiving reachability graphs.

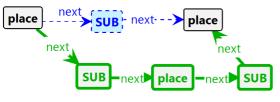

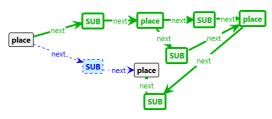

We applied this technique to our example. The example contains two hammocks. First includes all vertexes and tranAlgorithm 2: Modular construction of Time Petri net reachability graph

| begin                                                     |

|-----------------------------------------------------------|

| Let $H$ be the set of hammocks in the net;                |

| $X := \emptyset;$                                         |

| foreach $h \in H$ do                                      |

| <b>foreach</b> Transition $t \in h$ do                    |

| <b>Insert</b> $eft(t)$ into X;                            |

| <b>Insert</b> $lft(t)$ into X;                            |

| $GCD_h$ =Find GCD(X);                                     |

| <b>foreach</b> Transition $t \in h$ do                    |

| $T'_h = \{t'   t \in T_h \land eft(t') =$                 |

| $e \tilde{f}t(t)/GCD_h \wedge lft(t') = lft(t)/GCD_h \};$ |

| $h' = (P_h, T'_h, F, V)$                                  |

| <b>Apply Algorithm 1 to</b> <i>h</i>                      |

sitions between places *start1* and *end1* inclusively. Second starts at place *start2* and ends with *end2*. We can predict the successful application of the modular approach as the GCD of the first hammock time specifications is 3 and the GCD of the second hammock is 5, which are coprime numbers. Then we applied 2 and received the following results Table I.

The reachability graph of the whole net consists of 208 vertexes and 907 edges. But if we split up the net into 2 hammocks and then construct reachability graph for each of them, then the sum of them will be much lesser than the reachability graph of the whole net. In our case, the original net's reachability graph is not very big, because it is just an example, but even here reduction is significant.

TABLE I. ORIGINAL AND MODIFIED ALGORITHMS COMPARISON

|                      | Vertexes | Edges |

|----------------------|----------|-------|

| Original (full net)  | 208      | 907   |

| Modified (hammock 1) | 8        | 14    |

| Modified (hammock 2) | 7        | 9     |

#### VII. CONCLUSION

In this paper we provided an example Time Petri net that models the process of an academic course. The numeric properties of the transitions time specifications and our modification of the algorithm enabled us decrease time and space requirements for the analysis of the net. We constructed a reachability graph that is much smaller than the original one. The further research directions are to characterize the class of time Petri nets and the behavioural properties for which such technique is applicable.

#### ACKNOWLEDGMENT

This study was carried out within the National Research University Higher School of Economics' Academic Fund.

#### References

B. Bérard, F. Cassez, S. Haddad, D. Lime, and O. H. Roux. Comparison of different semantics for time petri nets. In *ATVA*, pages 293–307, 2005.

- [2] B. Berthomieu, M. Boyer, and M. Diaz. Time petri nets. In *Petri Nets*, pages 123–161.

- [3] H. Genrich and K. Lautenbach. The Analysis of Distributed Systems by means of Predicate/Transition-Nets. In G. Kahn, editor, *Semantics* of Concurrent Compilation, volume 70 of Lecture Notes in Computer Science, pages 123–146. Springer-Verlag, Berlin, 1979.

- [4] K. Jensen and L. M. Kristensen. *Coloured Petri nets: modelling and validation of concurrent systems.* Springer, 2009.

- [5] L. Lamport. What good is temporal logic? In *IFIP Congress*, pages 657–668, 1983.

- [6] I. A. Lomazova. Nested petri nets for adaptive process modeling. In Pillars of computer science, pages 460–474. Springer, 2008.

- [7] I. A. Lomazova. Interacting workflow nets for workflow process reengineering. *Fundamenta Informaticae*, 101(1):59–70, 2010.

- [8] S. S. Owicki and L. Lamport. Proving liveness properties of concurrent programs. ACM Trans. Program. Lang. Syst., 4(3):455–495, 1982.

- [9] L. Popova-Zeugmann. *Essential states in time Petri nets*. Citeseer, 1998.

- [10] L. Popova-Zeugmann. Time Petri Nets. Springer, 2013.

- [11] C. Ramchandani. Analysis of asynchronous concurrent systems by timed petri nets. 1974.

- [12] M. Schiffers and H. Wedde. Analyzing program solutions of coordination problems by cp-nets. In J. Winkowski, editor, *Mathematical Foundations of Computer Science 1978*, volume 64 of *Lecture Notes in Computer Science*, pages 462–473. Springer Berlin Heidelberg, 1978.

# On the deadlock control in parallel resource-constrained workflows

Vladimir A. Bashkin and Nadezhda Yu. Panfilova Yaroslavl State University Yaroslavl, Russia 150000 Email: v\_bashkin@mail.ru lillian007@mail.ru

Abstract—We study the verification of the soundness property for workflow nets extended with resources. A workflow is sound if it terminates properly (no deadlocks and livelocks are possible). A class of resource-constrained workflow nets (RCWF-nets) is considered, where resources can be used by a process instance, but cannot be created or spent.

Two sound RCWF-net, using the same set of resources, can be put in parallel. This parallel composition in some cases may produce additional deadlocks. A problem of deadlock avoidance in parallel workflows is studied, some methods of deadlock search and control are presented.

Keywords—Petri net, workflow, soundness, deadlock, RCWFnet, parallel composition

#### I. INTRODUCTION

Workflow management systems provide the automated support and coordination of business and technological processes to reduce costs and flow times and to increase quality of service and productivity. Workflows orchestrate people, resources, technology and information flow. Workflow nets [1], [2], a particular class of Petri nets, have become one of the standard ways to model and analyze workflow processes.

Workflow net is an abstraction of the workflow that can be used to check the so-called soundness property. This property guarantees the absence of livelocks, deadlocks, and other anomalies that can be detected without domain knowledge. Nowadays there exists a number of soundness notions (see [3] for a survey). Informally, the classical soundness ensures that from any reachable state the system may terminate properly.

A workflow consists of a set of coordinated tasks describing the flow of work within the organization. In real world the occurrence of those tasks may depend on resources, such as machines, manpower, and raw material. To take resources into account different extensions of a base formalism of WF-nets have been introduced, coursing different versions of soundness.

In [4], [5] a specific class of WFR-nets with decidable soundness was studied. In [10], [12] a more general class of Resource-Constrained Workflow Nets (RCWF-nets) was defined. Informally, the authors impose two constraints on resources. First, they require that all resources that are initially available are available again after terminating of all cases. Second, they also require that for any reachable marking, the number of available resources does not override the number of initially available resources. In [6], [7] a more general case of arbitrary resource transformations was studied.

In [10] it was proven that for RCWF-nets with a single resource type generalized soundness can be effectively checked in polynomial time. In [12] it was proven that generalized soundness is decidable in RCWF-nets with an arbitrary number of resource places (by reducing to the home-space problem).

Although soundness is decidable, there is so far no efficient decision algorithm because the proposed algorithm decides a home-space property, which requires a finite but (in general) too high number of reachability checks [12]. In addition, the problem of the calculation of the smallest number of resources for which soundness can be proved, remains open.

In this paper we consider a compositional approach to this problem. We investigate possible ways of minimal resource partitioning in control-independent and resource-dependent parallel branches of a workflow. We define a natural notion of parallel composition of two RCWF-nets, sharing common resource places. Parallelism may introduce additional deadlocks here, but we prove that these deadlocks (and other soundness violations) are avoidable by an enlargement of the initial resource. We present an approach, that allows to compute a nontrivial subset of minimal sound resources of a decomposable RCWF-net.

The main result of the paper is a method of deadlock avoidance for parallel workflows. We show that under certain circumstances a composite workflow can be restructured in such a way that the resulting net would require not a sum but a union of minimal sound resources of its parallel subnets. This allows to save a significant part of resources without any violation of the soundness property.

The paper is organized as follows. In Section 2 basic definitions of multisets and Petri nets are given. In Section 3 resource-constrained workflow nets and their soundness properties are formally defined. In Section 4 we study reachability properties of sound RCWF-nets. In Section 5 a notion of parallel composition of RCWF-nets is introduced. Several result are formulated, describing how minimal resources of a composite workflow can be obtained from minimal resources of its parallel subnets. In Section 6 deadlock/livelock avoidance methods are presented. The first one can be applied for any pair of sound workflows, but requires specific run-time control, not incorporated into the net itself. The second one uses the

original Petri net structure, but is applicable to the safe nets only. Section 7 contains some conclusions.

#### II. PRELIMINARIES

Let S be a finite set. A *multiset* m over a set S is a mapping  $m : S \rightarrow Nat$ , where Nat is the set of natural numbers (including zero).

For two multisets m, m' we write  $m \subseteq m'$  iff  $\forall s \in S : m(s) \leq m'(s)$  (the inclusion relation). The sum and the union of two multisets m and m' are defined as usual:  $\forall s \in S : m+m'(s) = m(s)+m'(s), m \cup m'(s) = max(m(s), m'(s))$ . By  $\mathcal{M}(S)$  we denote the set of all finite multisets over S.

Let P and T be disjoint sets of *places* and *transitions* and let  $F : (P \times T) \cup (T \times P) \rightarrow Nat$ . Then N = (P, T, F) is a *Petri net*. A *marking* in a Petri net is a function  $M : P \rightarrow Nat$ , mapping each place to some natural number (possibly zero). Thus a marking may be considered as a multiset over the set of places. Pictorially, P-elements are represented by circles, T-elements by boxes, and the flow relation F by arcs. Places may carry tokens represented by filled circles.

For a transition  $t \in T$  the preset  $\bullet t$  and the postset  $t^{\bullet}$  are defined as the multisets over P such that  $\bullet t(p) = F(p, t)$  and  $t^{\bullet}(p) = F(t, p)$  for each  $p \in P$ . Similarly, for a place  $p \in P$  we define  $\bullet p$  and  $p^{\bullet}$  as the multisets over T such that  $\bullet p(t) = F(t, p)$  and  $p^{\bullet}(t) = F(p, t)$  for each  $t \in T$ .

A transition  $t \in T$  is enabled in a marking M iff  $\forall p \in P \ M(p) \geq F(p,t)$ . An enabled transition t may fire yielding a new marking  $M' =_{def} M - {}^{\bullet}t + t^{\bullet}$ , i. e. M'(p) = M(p) - F(p,t) + F(t,p) for each  $p \in P$  (denoted  $M \xrightarrow{t} M'$ , or just  $M \to M'$ ). We say that M' is reachable from M iff there is a sequence  $M = M_1 \to M_2 \to \cdots \to M_n = M'$ . For a Petri net N by  $\mathcal{R}(N, M_0)$  we denote the set of all markings reachable from its initial marking  $M_0$ .

A net  $(N, M_0)$  is bounded iff  $\mathcal{R}(N, M_0)$  is finite.

A net  $(N, M_0)$  is *safe* iff  $\forall M \in \mathcal{R}(N, M_0), p \in P$  we have  $M(p) \leq 1$ . Places in safe nets can be considered as boolean variables (no tokens – false, 1 token – true).

#### III. RCWF-NETS

A resource-constrained workflow net (RCWF-net for short) is a tuple  $N = (P_c, P_r, T, F_c, F_r, i, o)$  s.t.

- $P_c$  is a finite set of control places;

- $P_r$  is a finite set of resource places,  $P_c \cap P_r = \emptyset$ ;

- T is a finite set of transitions,  $P_c \cap T = P_r \cap T = \emptyset$ ;

- $F_c$  :  $(P_c \times T) \cup (T \times P_c) \rightarrow Nat$  is a multiset of control arcs;

- $F_r$  :  $(P_r \times T) \cup (T \times P_r) \rightarrow Nat$  is a multiset of resource arcs;

- $\forall t \in T \exists p \in P_c : F_c(p,t) + F_c(t,p) > 0$  (each transition is incident to some control place);

- *i* ∈ *P<sub>c</sub>* is a source place and *o* ∈ *P<sub>c</sub>* is a sink place (input and output), such that <sup>•</sup>*i* = *o*<sup>•</sup> = Ø;

• every node from  $P_c \cup T$  is on a path from *i* to *o*, and this path consists of nodes from  $P_c \cup T$ .

In RCWF-nets Petri net places are divided into control and resource ones. Note that all transitions are necessarily linked to control places — this guarantees the absence of "uncontrolled" resource modifications.

A marking is also divided into control and resource parts. For a multiset c + r, where  $c \in \mathcal{M}(P_c)$  and  $r \in \mathcal{M}(P_r)$ , we write c|r.

For a net N a resource is a multiset over  $P_r$ . A controlled resource (a state) is a multiset over  $P_c \cup P_r$ .

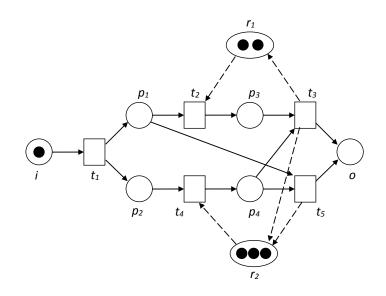

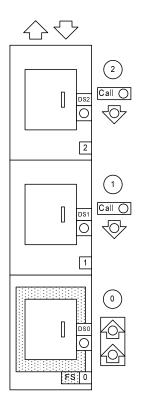

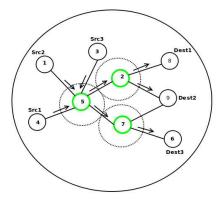

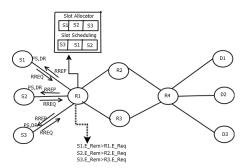

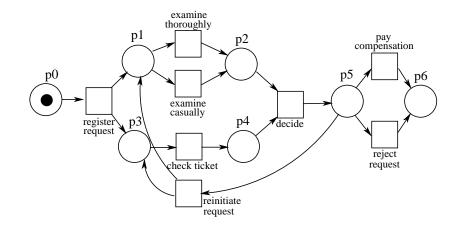

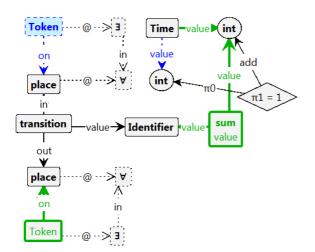

Fig. 1 represents an example of a RCWF-net, where resource places  $r_1$  and  $r_2$  are depicted by ovals, resource arcs — by dotted arrows.

Every RCWF-net  $N = (P_c, P_r, T, F_c, F_r, i, o)$  contains its *control subnet*  $N_c = (P_c, T, F_c, i, o)$ , which forms a RCWF-net with the empty set of resources.

A marked net (N, i|r) is a net N together with some initial marking i|r (here *i* denote a multiset, containing a single token in the input place *i*).

Let N be an RCWF-net. N is (r)-sound for some resource  $r \in \mathcal{M}(P_r)$  iff  $\forall c | r' \in \mathcal{R}(N, i | r)$  we have:

1)  $r' \leq r;$ 2)  $o|r \in \mathcal{R}(N, c|r').$

N is sound iff there exists some resource  $r \in \mathcal{M}(P_r)$  such that N is (r')-sound for any  $r' \geq r$ .

For example, the net on Fig. 1 is sound,  $(r_1 + r_2)$ -sound and not  $(r_1)$ -sound.

Thus soundness for an RCWF-net means, that, first, this workflow net can terminate properly from any reachable state, and, moreover, adding any extra resource does not violate the proper termination property. In [12] it was proven that the soundness problem is decidable even in a more general case of multiple input tokens.

Definition 1: For a sound RCWF-net N by res(N) and mres(N) we denote the sets of sound and minimal sound resources:

•

$$\operatorname{res}(N) =_{\operatorname{def}} \{r \in \mathcal{M}(P_r) \mid N \text{ is } (r+r') -$$

sound for any  $r' \in \mathcal{M}(P_r)\};$

•  $\operatorname{mres}(N) =_{\operatorname{def}} \{ r \in \operatorname{res}(N) \mid \exists r' \in \operatorname{res}(N) : r' < r \}.$

Obviously, mres(N) is finite.

For example, for the net on Fig. 1 we have  $mres(N) = \{r_1 + r_2\}$ .

As it was stated in [12], the problem of finding mres(N) is still open. In this paper we introduce and evaluate a promising approach to this problem, based on the parallel composition/decomposition of RCWF-nets.

#### IV. PROPERTIES OF SOUND RESOURCES

The next statement formally defines a well-known "proper completion" property of sound workflows:

Fact 1: For any (r)-sound net N

$$c|r \in \mathcal{R}(N, i|r) \Rightarrow c = o \lor c \cap o = \emptyset.$$

*Proof:* Assume the converse:  $o + m | r \in \mathcal{R}(N, i | r)$  for some non-empty m.

From the second requirement of soundness we have  $o|r \in \mathcal{R}(N, o + m|r)$ . However, since the place o doesn't have outgoing arcs, we have  $\emptyset|r \in \mathcal{R}(N, m|r)$ . But every transition in N has at least one *output* control place, thus  $m = \emptyset$  — a contradiction.

Another established fact is the soundness and boundedness of the control subnet:

Fact 2: For any sound RCWF-net  $N = (P_c, P_r, T, F_c, F_r, i, o)$  and its control subnet  $N_c = (P_c, T, F_c, i, o)$  (that may be considered as an RCWF-net with an empty set of resources) we have:

1)  $N_c$  is ( $\emptyset$ )-sound;

2)  $(N_c, i|\emptyset)$  is bounded;

3) if  $c|\emptyset, c+c'|\emptyset \in \mathcal{R}(N, i|r)$  then  $c' = \emptyset$ .

**Proof:** (1) Assume the converse:  $N_c$  is not  $(\emptyset)$ -sound. Since  $N_c$  contains no resource places, only the second part of the soundness definition is violated:

$$\exists c | \emptyset \in \mathcal{R}(N_c, i | \emptyset) : o | \emptyset \notin \mathcal{R}(N_c, c | \emptyset).$$

Denote the corresponding transition sequence by  $\sigma$  (so we have  $i|\emptyset \xrightarrow{\sigma} c|\emptyset$ ).

Now consider N. Obviously, there exists some large initial resource r s.t.  $c|r' \in \mathcal{R}(N, i|c)$  for some r' — it is sufficient to sum all resources, required by transitions of  $\sigma$ .

On the other hand, no resource x would be enough to reach the final state o|y from c|x (for any y), since it is unreachable even in the "resource-free" control subnet  $N_c$ . Hence N is not sound.

(2) Otherwise an infinite run is possible in  $(N_c, i|\emptyset)$ , containing an infinite number of different markings, and hence a pair of markings  $c_1 < c_2$  with  $i \to c_1 \to c_2 \to \ldots$ . From the soundness of  $N_c$  we have  $c_1 \xrightarrow{\sigma} o$  for some sequence of transitions  $\sigma \in T^*$ . But from  $c_1 < c_2$  the same sequence is possible in  $c_2 : c_2 \xrightarrow{\sigma} o + (c_2 - c_1)$  — a contradiction to the proper completion property.

(3) Assume the converse. From the soundness property we have two transition sequences:  $i|\emptyset \to c|\emptyset \to o|\emptyset$  and  $i|\emptyset \to c + c'|\emptyset \to o|\emptyset$ .

From the first sequence and the monotonicity of Petri nets we have  $i + c'|\emptyset \to c + c'|\emptyset \to o + c'|\emptyset$ . Combining with the second sequence, we obtain  $i|\emptyset \to c + c'|\emptyset \to o + c'|\emptyset$  — a contradiction to the soundness property.

Every reachable  $c \in \mathcal{M}(P_r)$  (a *control state* of a control subnet  $N_c$ ) corresponds to a single reachable resource value:

Lemma 1: If N is sound,  $r \in \operatorname{res}(N)$  and  $c|r_1, c|r_2 \in \mathcal{R}(N, i|r)$ , then  $r_1 = r_2$ .

*Proof:* Assume the converse: let  $r_1 \neq r_2$ .

Consider some  $r' = r_1 + \delta_1 = r_2 + \delta_2$ . From  $r_1 \neq r_2$  we have  $\delta_1 \neq \emptyset$  or  $\delta_2 \neq \emptyset$  or both. Additionally,  $\delta_1 \neq \delta_2$ .

We have  $i|r \to c|r_1 \to o|r$  and hence (from the monotonicity of Petri nets)  $i|r + \delta_1 \to c|r_1 + \delta_1 \to o|r + \delta_1$ . Similarly,  $i|r+\delta_2 \to c|r_2+\delta_2 \to o|r+\delta_2$ . But  $r_1+\delta_1 = r' = r_2+\delta_2$  and hence we have  $i|r+\delta_1 \to c|r' \to o|r+\delta_2$ . From the  $(r+\delta_1)$ soundness property it should be  $\delta_1 = \delta_2$  — a contradiction.

Note that we cannot replace in the statement of Lemma 1 " $r \in \operatorname{res}(N)$ " by "N is (r)-sound", because an (r)-sound net is not necessarily  $(r + \delta)$ -sound.

For (r)-soundness we have a weaker property:

Lemma 2: If N is (r)-sound and  $c|r_1,c|r_2 \in \mathcal{R}(N,i|r)$ , then

$r_1 \not< r_2$  and  $r_1 \not> r_2$ .

*Proof:* Similar to the previous Lemma. Assume the converse:  $r_1 < r_2$  and hence  $r_2 = r_1 + \delta_1$  with  $\delta_1 \neq \emptyset$ .

We have  $i|r \to c|r_1 \to o|r$  and  $i|r \to c|r_2 = c|r_1 + \delta_1 \to o|r$ , and so  $c|r_1 + \delta_1 \to o|r + \delta_1 - a$  contradiction to the (r)-soundness.

Since any set of incomparable vectors over  $Nat^{|P_r|}$  is finite, we have an obvious

Corollary 1: If N is (r)-sound then  $\mathcal{R}(N, i|r)$  is finite.

A particular consequence of Lemma 1 is an inability of a cycle to modify a resource:

Proposition 1: If N is sound,  $r \in \operatorname{res}(N)$ ,  $c|r_1 \in \mathcal{R}(N, i|r)$  and  $c|r_2 \in \mathcal{R}(N, c|r_1)$ , then  $r_1 = r_2$ .

*Proof:* Immediately from Lemma 1.

Moreover, a sound net can perform only fixed resource transformations:

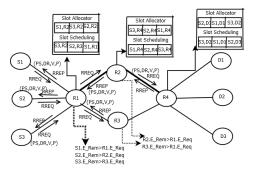

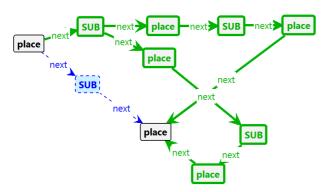

Fig. 2. Two examples of RCWF-nets compositions

Proposition 2: If N is sound,  $r \in \mathbf{res}(N), c|r' \in$  $\mathcal{R}(N, i|r)$  and  $u \in \mathcal{M}(P_r)$ , then for any  $c|v \in \mathcal{R}(N, i|r+u)$ we have v = r' + u.

*Proof:* Assume the converse. Hence  $c|v,c|r'+u \in$  $\mathcal{R}(N, i|r+u)$  with  $v \neq r'+u$  — a contradiction to Lemma 1.

#### V. COMPOSITIONS OF RCWF-NETS

Nets with the same sets of resource places can be composed in parallel:

Definition 2: Let  $N_1$  and  $N_2$  be RCWF-nets with

- $N_1 = ((P_c)_1, P_r, T_1, (F_c)_1, (F_r)_1, i_1, o_1)$  and

- $N_2 = ((P_c)_2, P_r, T_2, (F_c)_2, (F_r)_2, i_2, o_2).$

A parallel composition of  $N_1$  and  $N_2$  (denoted by N = $N_1 || N_2$ ) is an RCWF-net  $N = (P_c, P_r, \overline{T}, F_c, F_r, i, o)$  with

- $P_{c} =_{\text{def}} (P_{c})_{1} \cup (P_{c})_{2} \cup \{i, o\},\$

- $T =_{\operatorname{def}} T_1 \cup T_2 \cup \{t_i, t_o\},$ •

- $F_c =_{\text{def}} (F_c)_1 \cup (F_c)_2 \{(i,t_i), (t_i,i_1), (t_i,i_2), (t_o,o), (o_1,t_o), (o_2,t_o)\},\$ U

- $F_r =_{\operatorname{def}} (F_r)_1 \cup (F_r)_2.$

We put two workflows in parallel, adding common source and sink places.

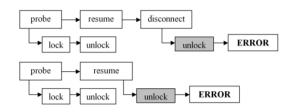

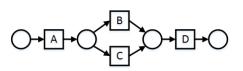

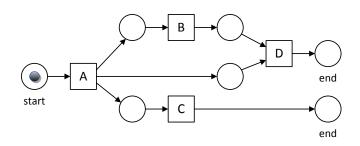

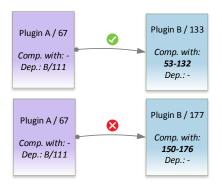

Examples of simple RCWF-nets compositions are given on Fig. 2. In the case Fig. 2.(a) both subnets has the same minimal sound resource r, and the composition is also sound with this resource. The case Fig. 2(b) is quite different. Note that  $r_1 + r_2$  is a minimal sound resource for both subnets, but the composition is not  $(r_1 + r_2)$ -sound because of a deadlock  $p_1 + p_2 | \emptyset$ , reachable from  $i | r_1 + r_2$ . Any larger resource is sound.

Soundness of a resource for a subnet does not necessarily imply it's soundness for a composition (as one would expect, taking into account the conservativeness of resource transformations in an RCWF-net). A parallelism may introduce additional deadlocks. However, a simple kind of additive closure exists:

Theorem 1: If  $N_1$  and  $N_2$  are sound then  $N_1 || N_2$  is sound and, moreover:

- $r_1 \in \operatorname{res}(N_1), r_2 \in \operatorname{res}(N_2) \Rightarrow r_1 + r_2 \in$ 1)  $res(N_1 || N_2);$  $r \in \operatorname{res}(N_1 || N_2) \Rightarrow \exists r_1 \in \operatorname{res}(N_1) : r \leq r_1;$  $r \in \operatorname{rres}(N_1 || N_2) \Rightarrow \exists r_1 \in \operatorname{res}(N_1) : r \leq r_1.$ 2)

- 3)

*Proof:* The soundness itself and the first statement follows from Proposition 2. Note that subnets  $N_1$  and  $N_2$  here work independently, without interferencing into each other's "part" of the common resource.

To prove the second statement we can take  $r_1 = r$ : since a resource is sound for a parallel composition, it properly supports system runs of the form  $i|r \rightarrow i_1+i_2|r \rightarrow o_1+i_2|r \rightarrow$  $o_1 + o_2 | r.$

The third statement is a trivial consequence of the second one.

The first statement of Theorem 1 implies that

Corollary 2: If  $N_1$  and  $N_2$  are sound and  $r_1$  $\mathbf{mres}(N_1), r_2 \in \mathbf{mres}(N_2)$ , then there exists r $\in$  $\in$  $\operatorname{mres}(N_1 || N_2)$  such that  $r \leq r_1 + r_2$ .

So, to find some minimal resource r one may search through a finite number of resources, less then or equal to  $r_1 + r_2$ . For every candidate  $r' \leq r_1 + r_2$  the set  $\mathcal{R}(N, i|r')$  is finite (Corollary 1) and can be constructed by a finite number of steps.

Note that we have not proven that this method of minimal sound resources computation allows to compute ALL elements of  $mres(N_1 || N_2)$  (however, we believe it does). Nevertheless, the computed subset is always nonempty and nontrivial.

So, a problem of mres(N) calculation can be partially reduced to the same problem for subnets, composed in parallel. In most cases the process of decompositions ends with a purely sequentional workflows, which may have a very simple set of sound (and minimal sound) resources.

#### VI. SOUNDNESS ENSURING

In this section we consider a resource r, sound for both subnets but not sound for a parallel composition (like  $r_1$  +  $r_2$  in Fig. 2(b)). Note that such a resource always enables a non-empty set of "good" runs (at least two: i|r ightarrow  $i_1$  +  $i_2|r \to o_1 + i_2|r \to o_1 + o_2|r$  and  $i|r \to i_1 + i_2|r \to i_1 + i_3|r \to i_1|r \to i_1|$  $o_2|r \rightarrow o_1 + o_2|r)$ . Hence a resource is not worthless and it would be interesting to develop some control policies or system transformations, preserving all "good" runs and disabling all "bad" ones (without increasing the initial resource).

So we consider both kinds of possible undesirable (not properly terminating) behaviors of a Petri net, namely, deadlocks and livelocks.

A reachable marking c|r is a *deadlock state* iff  $c \neq o$  and there is no transition  $t \in T$  s.t.  $c|r \stackrel{t}{\to} c'|r'$  for some c', r'.

A finite set L of reachable markings is a *livelock* iff

- 1) |L| > 1;

- 2) for any  $c|r, c'|r' \in L$  there is a finite transition sequence  $\sigma \in T^*$  s.t.  $c|r \stackrel{\sigma}{\to} c'|r'$ ;

- 3) for any  $c|r \in L$  and  $t \in T$  s.t.  $c|r \xrightarrow{t} c''|r''$  we have  $c''|r'' \in L$ .

A *livelock state* is a state that belongs to some livelock.

Note that by definition  $o | r \notin L$  for any r.

By D(N, i|r) we denote a set of all deadlock and livelock states of a marked RCWF-net (N, i|r).

Theorem 2: If  $N = N_1 || N_2$  and  $r \in \operatorname{res}(N_1) \cap \operatorname{res}(N_2)$ then (N, i|r) is bounded (i.e.  $\mathcal{R}(N, i|r)$  is finite).

*Proof:* From the second statement of Fact 2 the sets of control markings are finite for both  $N_1$  and  $N_2$ . Obviously, the set of reachable control markings of N is a subset of a product of these two finite sets, hence it is also finite.

Now consider markings from  $\mathcal{R}(N, i|r)$ . Assume the converse — this set is infinite. Hence from the boundedness of the control subnet there exists some control cycle, strictly increasing the resource:  $i|r \rightarrow c_1 + c_2|r' \stackrel{\sigma}{\rightarrow} c_1 + c_2|r' + r''$  with  $c_1 \in \mathcal{M}((P_c)_1), c_2 \in \mathcal{M}((P_c)_2), \sigma \in T^*$  and  $r'' \neq \emptyset$ .

Recall that  $T = T_1 \cup T_2$  and denote by  $\sigma_1$  and  $\sigma_2$  the largest subsequences of  $\sigma$  s.t.  $\sigma_1 \in (T_1)^*$  and  $\sigma_2 \in (T_2)^*$ . Obviously,  $\sigma_1$  and  $\sigma_2$  are control cycles in  $N_1$  and  $N_2$  respectively.

From Proposition 1 neither  $\sigma_1$  nor  $\sigma_2$  can change the resource, hence their composition also cannot do this — a contradiction.

Since  $D(N, i|r) \subseteq \mathcal{R}(N, i|r)$  we have:

Corollary 3: If  $N = N_1 || N_2$  and  $r \in \operatorname{res}(N_1) \cap \operatorname{res}(N_2)$  then D(N, i|r) is finite.

So the set of deadlocks and livelocks is computable by a simple reachability set construction and search. A naive deadlock control policy would be to compute a set of all deadlocks/livelocks and all their predecessing states and to control them in run-time, not allowing a system to make the wrong "last step".

#### A. Safe nets

A rather interesting case are safe workflows, i.e. RCWFnets with safe control subnets (where none of the control places can accumulate more than one token). This is not a strong restriction, because every bounded net is weakly bisimilar to some safe net. Note that the net in Fig. 2(b) is safe and still has a deadlock. A safe RCWF-net has only ordinary control arcs:  $F_c(x, y) \leq 1$  for any x and y.

We can apply a transformation, eliminating all dead-locks/livelocks in a safe net:

Definition 3: Let  $N_1$  and  $N_2$  be sound safe RCWF-nets with the same set  $P_r$  of resource places, and let  $r \in \mathcal{M}(P_r)$ be a resource s.t.  $r \in \operatorname{res}(N_1)$  and  $r \in \operatorname{res}(N_2)$ .

Let  $N = N_1 || N_2 = (P_c, P_r, T, F_c, F_r, i, o)$  be a not-(r)-sound parallel composition of  $N_1$  and  $N_2$ .

By  $D_c(N, i|r)$  we denote the set of all different control parts of elements of D(N, i|r), and let  $Z = |D_c(N, i|r)|$  (obviously, we have Z > 0).

A net  $(N_a, i|r+v)$ , where  $N_a = (P_c, P_r \cup V, T, F_c, F_r \cup F_{in} \cup F_{out}, i, o)$ , is called a *controlled system* of (N, i|r) iff

- $V = \{v_k | k \in \overline{1, Z}\}$  is a set of additional "holding" places, with their number equal to the number of possible control deadlocks/livelocks in the net N;

- $F_{in}$  are input holding arcs such that  $F_{in} = \{(v_k, t) \mid F_c(t, p) = 1 \text{ for some } p \in d_k, \text{ where } d_k \text{ is a } k^{th} \text{ element of } D_c(N, i|r)\};$

- $F_{out}$  are output holding arcs such that  $F_{out} = \{(t, v_k) \mid F_c(p, t) = 1 \text{ for some } p \in d_k, \text{ where } d_k \text{ is a } k^{th} \text{ element of } D_c(N, i|r)\};$

- $v = (|d_1| 1)v_1 + (|d_2| 1)v_2 + \ldots + (|d_Z| 1)v_Z$ , where  $d_k$  is a  $k^{th}$  element of  $D_c(N, i|r)$ .

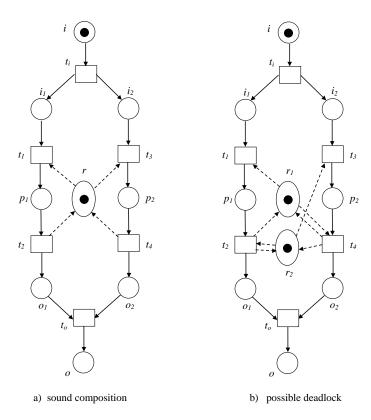

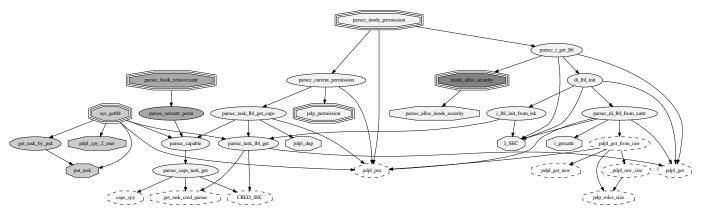

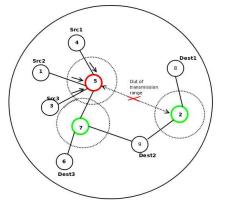

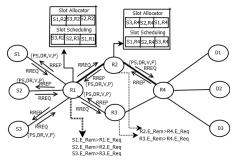

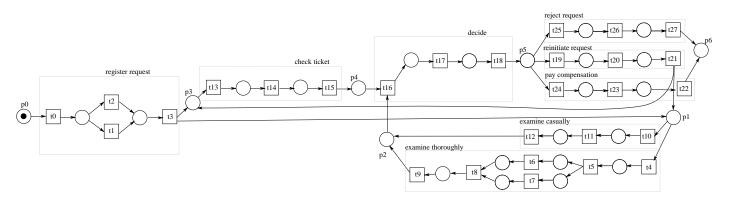

Main idea to start with is that we have to avoid the consequent triggering of transitions leading to deadlock/livelock places. Thus for every element of D(N, i|r) we include into the net a holding (restraining) place which resource will allow triggering of transitions leading to just one control place among them. Resource should be put back to holding place right after token leaves deadlock place. Implementation of this idea based on the net from Fig. 2 is shown on Fig. 3.

Note that the initial resource (r + v) is actually not an increased original initial resource r, since v is built over the new (additional) set of resource places.

Theorem 3: Let  $N_1$  and  $N_2$  be sound safe RCWF-nets with the same set  $P_r$  of resource places, and let  $r \in \mathcal{M}(P_r)$  be a resource s.t.  $r \in \operatorname{res}(N_1)$  and  $r \in \operatorname{res}(N_2)$ .

Let  $N = N_1 || N_2 = (P_c, P_r, T, F_c, F_r, i, o)$  be a not-(r)-sound parallel composition of  $N_1$  and  $N_2$ .

Let net  $(N_a, i|r+v)$  be the controlled system of the marked net (N, i|r). Then  $(N_a, i|r+v)$  is (r+v)-sound.

*Proof:* Obviously, none of the original deadlocks/livelocks is reachable (by construction).

Now we need to prove that no new deadlocks/livelocks are introduced.

Consider some deadlock/livelock  $c_1 + c_2 | r$  of the original net. From the third statement of Fact 2 and the safety property none of the control states of  $N_1$ , except  $c_1$  can have the same or larger total number of tokens in all places of  $c_1$  (similarly for the net  $N_2$  and places of  $c_2$ ). Hence  $|c_1+c_2|-1 = |c_1|+|c_2|-1$

Fig. 3. Examples of RCWF-nets compositions with deadlock control

tokens is enough for all control states except this particular deadlock/livelock — hence the corresponding holding place would not introduce any undesirable restriction.

#### VII. CONCLUSION

We presented two methods of deadlock/livelock avoidance for a restricted resource. The first one can be applied for any pair of sound workflows, but requires specific run-time control, not incorporated into the net itself. The second one uses the original Petri net structure, but is applicable to the safe nets only. The proposed technique is similar to a technique, studied in the area of Flexible Manufacturing Systems (see [9] for a classical result). However, the key difference is the possibility of parallel behaviours in subnets (in FMS each subnet is a simple sequential automaton).

Further research will consider the application of holding places techique to the general case of RCWF-nets. As it can be seen from some preliminary counterexamples, the method would possibly require some additional modifications.

The problem of exact mres(N) calculation is still open but it will be studied in the further research. We believe that our approach can be applied here, at least for large nontrivial subclasses of RCWF-nets. For example, we plan to study structured workflows [2], [8], that can be obtained from primitives by a set of algebraic operations, such as parallel and sequential compositions. Another interesting method of sound resource compositions was presented in [11] — based on algebraic expressions over multisets. Our method is not implemented in applications. However, we believe it can be used as a verification and/or optimization tool in workflow management systems. Basically, it may enable the elimination of specific deadlocks and livelocks, induced by incorrect (unverified) parallel composition of submodules.

#### REFERENCES

- W.M.P. van der Aalst. The Application of Petri Nets to Workflow Management. *The Journal of Circuits, Systems and Computers*, 8(1):21– 66, 1998.

- [2] W.M.P. van der Aalst, K.M. van Hee. Workflow Management: Models, Methods and Systems, MIT Press, 2002.

- [3] W.M.P. van der Aalst, K.M. van Hee, A.H.M. Hofstede, N. Sidorova, H.M.W. Verbeek, M. Voorhoeve, M.T. Wynn. Soundness of workflow nets: classification, decidability, and analysis, *Form. Asp. of Comp.*, 23(3):333–363, Springer, 2011.

- [4] K. Barkaoui, L. Petrucci. Structural Analysis of Workflow Nets with Shared Resources. In Proc. Workflow Management: Net-based Concepts, Models, Techniques and Tools (WFM98), volume 98/7 of Computing Science Reports, pages 82–95, Eidhoven University of Technology, 1998.

- [5] K. Barkaoui, R. Ben Ayed, Z. Sbaï. Workflow Soundness Verification based on Structure Theory of Petri Nets. *International Journal of Computing and Information Sciences*, Vol. 5, No. 1, 2007. P.51–61.

- [6] V. A. Bashkin, I. A. Lomazova. Resource equivalence in workflow nets. In *Proc. Concurrency, Specification and Programming, 2006*, volume 1, pages 80–91. Berlin, Humboldt Universitat zu Berlin, 2006.

- [7] V.A. Bashkin, I.A. Lomazova. Soundness of Workflow Nets with an Unbounded Resource is Decidable Joint Proc. of Petri Nets and Software Engineering (PNSE'13) and Modeling and Business Environments (ModBE'13). Milano, 2013. Vol. 989 of CEUR. 2013. P. 61–75.

- [8] P. Chrząstowski-Wachtel. Sound Markings in Structured Nets. In Proc. Concurrency, Specification and Programming, 2005, pages 71–85. Warsaw, Warsaw University, 2005.

- [9] J. Ezpeleta, J.-M. Colom, J. Martinez. A Petri Net Based Deadlock Prevention Policy for Flexible Manufacturing Systems. *IEEE Transactions* on *Robotics and Automation*, 11(2), 1995. P.173–184.

- [10] K. van Hee, A. Serebrenik, N. Sidorova, M. Voorhoeve. Soundness of Resource-Constrained Workflow Nets. In *Proc. ICATPN 2005*, volume 3536 of *Lecture Notes in Computer Science*, pages 250–267. Springer, 2005.

- [11] I.A. Lomazova, I.V. Romanov. Analyzing Compatibility of Services via Resource Conformance. *Fundamenta Informaticae*, Vol. 128, No. 1–2, 2013. P.129–141.

- [12] N. Sidorova, C. Stahl. Soundness for resource-contrained workflow nets is decidable. *IEEE Transactions on Systems, Man, and Cybernetics: Systems*, 43(3), 2013. P.724–729.

# LTL-specification, verification and construction of PLC programs

Ryabukhin D. A. Yaroslavl State University Yaroslavl, Russia Email: dmitriy\_ryabukhin@mail.ru Kuzmin E. V. Yaroslavl State University Yaroslavl, Russia Email: kuzmin@uniyar.ac.ru

Abstract—An approach to specification, verification and construction of PLC programs for discrete problems is proposed. For the specification of the program behavior, we use the linear-time temporal logic LTL. Programming is carried out in ST, IL and LD languages according to an LTL-specification. The correctness analysis of an LTL-specification is carried out by the symbolic model checking tool Cadence SMV. A new approach to PLCprogramming is shown by an example. For a discrete problem, we give an ST-program, its LTL-specification and an SMV-model.

#### I. INTRODUCTION

Application of programmable logic controllers (PLCs) for systems controling complex industrial processes makes exacting correctness demands to PLC-programs. Any software error is considered to be inadmissible. However, the existing development tools for programming PLC, for example widely known CoDeSys (Controller Development System) [8], provide only usual debugging facilities through testing programs (not guaranteeing total absence of errors) by means of a visualization of PLC-control objects. At the same time certain theoretical knowledge and experience of applying the existing developments in the field of formal methods of modeling and analysis of software systems are accumulated. The programming of logical controllers is a practical area, in which existing developments could have successful application. Successful application is understood as implementation of formal methods in the process of program design at the level of a well-functioning technology which is clear to all specialists involved in this process - engineers, programmers and testers. Being as usual of a small size and having a finite state space, PLC-programs are exceptionally convenient objects for the formal (including automatic) analysis of correctness.

Programmable Logic Controllers (PLCs) are a special type of a computer widely used in automation systems [10], [5]. A PLC is a reprogrammable computer, based on sensors and actors, which is controlled by a user program. They are highly configurable and thus are applied to various industrial sectors. A PLC is a reactive system. A PLC repeats the execution of a user program periodically. There are three main phases for program execution (working cycle): 1) reading from inputs (sensors) and latching them in the memory, 2) program execution (with input variables remaining constant), 3) latching the values of the output variables to the environment. Programming languages for logic controllers are defined by the IEC 61131-3 standard. This standard includes the description of five languages: SFC, IL, ST, LD and FBD.

IL (Instruction List) is an assembly language with an accumulator and jumps to labels. IL allows to work with any data types, to call functions and function blocks, written in IEC 61131-3 standard languages. IL is used to build small components, when critical control is required. Instructions are executed with the accumulator content. The IL accumulator is a universal container, which can keep values of any type.

ST (Structured Text) is high-level programming language. Its syntax is the adapted Pascal syntax.

LD (Ladder Diagram) represents a program by a graphical diagram based on circuit diagrams of relay logic hardware. The language itself can be seen as a set of connections between logical checkers (contacts) and actuators (coils). If a path can be traced between the left side of the connection and the output, through asserted contacts, the output coil storage bit is asserted true. If no path can be traced, the output is false.

This languages provides a possibility of application of all existing methods of program correctness analysis — testing, theorem proving [9] and model checking [7] — for verification of PLC-programs. Theorem proving is more applicable to "continuous" stability and regulation problems of the engineering control theory, since an implementation of these problems in PLC is associated with programming of an appropriate system of formulas. Model checking is most suitable for "discrete" problems of logical control, requiring PLCs with binary inputs and outputs. This provides a finite space of possible states of PLC-programs.

The most convenient for programming, specification and verification of PLC-programs are ST, LD and SFC languages, since they do not cause difficulties for neither developers nor engineers and can be easily translated into languages of software tools of automatic verification.

Earlier in the article [2], a review of methods and approaches to programming "discrete" PLC problems was carried out on languages LD, SFC and ST. For these approaches the usability of the model checking method for the analysis of program correctness with respect to the automatic verification tool Cadence SMV [13] was evaluated. Some possible PLC-program vulnerabilities arising at traditional approaches to programming of PLC was revealed. In particular, existing

articles relating to correctness analysis of PLC programs [3], [6], [11], [12] is mainly devoted to construction of translators from IEC 61131 standard languages to interface languages of verification software. Demonstration of results is carried out on trivial examples. However, our experience of working with the practical logic control problems showed that the direct translation does nothing for analysis of program properties, since it is often not possible to express desired properties in temporal logic languages.

In this article, an approach to construction and verification of PLC-programs for discrete problems is proposed. For the specification of the program behavior, we use the linear-time temporal logic LTL. Programming is carried out in ST, IL and LD languages according to an LTL-specification. The correctness analysis of an LTL-specification is carried out by the symbolic model checking tool Cadence SMV. A new approach to programming and verification of PLC-programs is shown by an example. For a discrete problem we give an ST-program, its LTL-specification and an SMV-model. The purpose of the article is to describe an approach to programming PLC, which would provide a possibility of PLCprogram correctness analysis by the model checking method.

The further work is to build software tools for modeling, specification, construction and verification of PLC-programs.

#### II. MODEL CHECKING. A PLC PROGRAM MODEL

Model checking is the process of checking whether a given model (a Kripke structure) satisfies a given logical formula. A Kripke structure represents the behaviour of a program. A temporal logic formula encodes the property of the program. We use the linear-time temporal logic (LTL).

A Kripke Structure on a set of atomic propositions P is a state transition system  $S = (S, s_0, \rightarrow, L)$ , with a non-empty set of states S, an initial state  $s_0 \in S$ , a transition relation  $\rightarrow \subseteq S \times S$  which is defined for all  $s \in S$ , and a function  $L : S \rightarrow 2^P$ , labeling every state by a subset of atomic propositions.

A Path of the Kripke structure from the state  $s_0$  — is an infinite consequence of states  $\pi = s_0 s_1 s_2 \dots$  where  $\forall i \ge 0$   $s_i \rightarrow s_{i+1}$ .

The linear-time temporal logic language is considered as a specification language for behavioural properties of a programming model. PLC is a classic reactive control system, which once running must always have a correct infinite behavior. LTL formulas allow to represent this behavior.

The syntax of the LTL formula is given by the following grammar,  $p_i \in P$ :

$$\varphi, \psi ::= true \mid p_0 \mid p_1 \mid \dots \mid p_n \mid \neg \varphi \mid \psi \land \varphi \mid$$

$$X\varphi \mid \psi U\varphi \mid F\varphi \mid G\varphi.$$

LTL formula describes a property of one path of the Kripke structure, descendant from an emphasized current state. The temporal operators X, F, G and U are interpreted as follows:  $X\varphi - \varphi$  must hold at the next state,  $F\varphi - \varphi$  must hold at some future state,  $G\varphi - \varphi$  must hold at the current state and all future state,  $\psi U \varphi - \varphi$  holds at the current or a future

state, and  $\psi$  must hold up until this point. In addition, classical logical operators  $\lor$  and  $\Rightarrow$  will be used further.

The Kripke structure satisfies an LTL formula (property)  $\varphi$ , if  $\varphi$  holds true for all paths, starting from the initial state  $s_0$ .

The Kripke model for a PLC program can be built quite naturally. For a state of the model we take a vector of values of all program variables, which can be divided into two parts. The first part is a value vector of inputs at the moment of the beginning of a new PLC working cycle. The second part is a value vector of outputs and internal variables after passing a complete working cycle (on the inputs from the first part). In other words, the state of the model is a state of a PLCprogram after the complete passing of a working cycle. Thus, a transition from one state to another depends on the (previous) values of the outputs and internal variables of the first state and the (new) values of the inputs of the second state. For each state, the degree of the transition relation branching is determined by the number of all possible combinations of PLC input signals. Atomic propositions of the model are logical expressions on PLC program variables with using arithmetic and relational operators.

#### III. PROGRAMMING CONCEPT

A purpose of the article is to describe an approach to programming PLC, which would provide a possibility of PLCprogram correctness analysis by the model checking method. We will proceed from convenience and simplicity of using the model checking method. We require holding two following conditions.

*Condition* 1. The value of each variable must not change more than once per one full execution of the program while passing the PLC working cycle.

*Condition* 2. The value of each variable must change at only one place in the program in some operation block without nestings.

This conditions are reasonable assumption because inputs are always latched while operating the cycle. We will change the variable value only when it is really necessary, i. e. we will forbid an access to the variable by assigning if conditions of mandatory changing of its value do not hold. In this approach, the requirements of changing the value of a certain variable V after one pass of the PLC working cycle are represented by the following LTL formulas.

The next LTL formula is used for describing situations, leading to an increase of the variable value V

$$\mathbf{GX}(V \ge V \Rightarrow OldValCond \land FiringCond \land V = NewValExpr)(1)$$

This formula means that whenever a new value of variable V is larger than its previous value, recorded in the variable  $\_V$ , it follows that the old value of variable V satisfies the condition OldValCond, a condition of the external action FiringCond is accomplished, and the new value of variable V is the value of the expression NewValExpr.

The leading underscore symbol "\_" in the denotation of the variable  $_V$  is taken as a pseudo-operator, allowing to refer to

the previous state value of a variable V. This pseudo-operator can be used only under the scope of the temporal operator X.

Conditions *FiringCond* and *OldValCond* are logical expressions on program variables and constants, which are constructed using comparison operators, logical and arithmetic operators and the pseudo-operator "\_". By definition, the pseudo-operator can be applied only to variables. The expression *FiringCond* describes situations, when changing the value of the variable V is needed (if it is allowed by the condition *OldValCond*). The expression *NewValExpr* is built using variables and constants, comparison, logical and arithmetic operators and the pseudo-operator "\_".

For descriptions of all possible increasing value situations the formula (1) may have several sets of considered conjunctive parts  $OldValCond_i \wedge FiringCond_i \wedge V = NewValExpr_i$ , combined in a disjunction, after the operator  $\Rightarrow$ .

Situations that lead to a decrease of V value are described similarly:

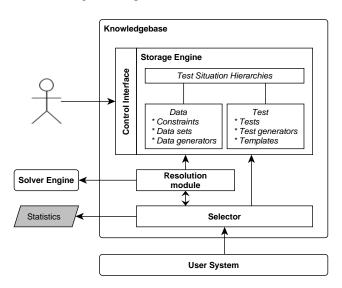

$$\mathbf{GX}(V < V \Rightarrow OldValCond' \land FiringCond' \land V = NewValExpr')(1')$$