# SYRCoSE 2011

## Editors:

## Alexander Kamkin, Alexander Petrenko, Andrey Terekhov

Proceedings of the 5<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering

Yekaterinburg, May 12-13, 2011

Yekaterinburg 2011

# **Proceedings of the 5<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE 2011)**, May 12-13, 2011 – Yekaterinburg, Russia:

The issue contains the papers presented at the 5<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE 2011) held in Yekaterinburg, Russia on 12<sup>th</sup> and 13<sup>th</sup> of May, 2011. Paper selection was based on a competitive peer review process being done by the program committee. Both regular and research-in-progress papers were considered acceptable for the colloquium.

The topics of the colloquium include system programming; static verification and analysis of programs; programming languages, methods and tools; testing of software and hardware systems; automata theory; computer graphics and others.

# **Труды 5-ого весеннего/летнего коллоквиума молодых исследователей в области программной инженерии (SYRCoSE 2011)**, 12-13 мая 2011 г. – Екатеринбург, Россия:

Сборник содержит статьи, представленные на 5-ом весеннем/летнем коллоквиуме молодых исследователей в области программной инженерии, проводимом в Екатеринбурге 12-13 мая 2011 г. Отбор статей производился на основе рецензирования материалов программным комитетом. На коллоквиум допускались как полные статьи, так и краткие сообщения, описывающие текущие исследования.

Программа коллоквиума охватывает следующие темы: системное программирование; статическая верификация и анализ программ; языки, методы и инструменты программирования; тестирование программных и аппаратных систем; теория автоматов; компьютерная графика и другие.

ISBN 978-5-91474-017-4

## Contents

| Foreword5                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Committees / Referees                                                                                                                                      |

| Guest Talk                                                                                                                                                 |

| Crowdsourcing Projects for Research, Education and Better Life<br><i>R. Yavorskiy</i>                                                                      |

| Biomolecular Computing                                                                                                                                     |

| tRNA Computing Units and Programming Languages<br>N. Odincova, V. Popov                                                                                    |

| System Programming                                                                                                                                         |

| Using Hardware-Assisted Virtualization to Protect Application Address Space Inside Untrusted<br>Environment<br>D. Silakov                                  |

| Background Optimization in Full System Binary Translation<br><i>R. Sokolov, A. Ermolovich</i> 25                                                           |

| The ARTCP Header Structure, Computation and Processing in the Network Subsystem of Linux Kernel<br>A. Sivov, V. Sokolov                                    |

| Information Representation, Search and Reasoning                                                                                                           |

| A New Double Sorting-Based Node Splitting Algorithm for R-Tree<br>A. Korotkov                                                                              |

| Fuzzy Matching for Partial XML Merge<br>V. Fedotov                                                                                                         |

| High-level Data Access Based on Query Rewritings<br><i>E. Stepalina</i>                                                                                    |

| Application of the Functional Programming Tools in the Tasks of Language and Interlanguage Structures<br>Representation<br><i>P. Ermakov, O. Kozhunova</i> |

| Static Verification and Analysis of Programs                                                                                                               |

| Static Verification Under The Hood: Implementation Details and Improvements of BLAST<br>P. Shved, V. Mutilin, M. Mandrykin                                 |

| Detecting C Program Vulnerabilities<br>A. Ermakov, N. Kushik                                                                                               |

| Model Checking Approach to the Correctness Proof of Complex Systems<br><i>M. Alekseeva, E. Dashkova</i>                                                    |

## Programming Languages, Methods and Tools

| Thorn Language: a Flexible Tool for Code Generation      Y. Okulovsky                                          |

|----------------------------------------------------------------------------------------------------------------|

| One Approach to Aspect-Oriented Programming Implementation for the C Programming Language<br><i>E. Novikov</i> |

| Component-Based Software Engineering and Runtime Type Definition<br>A. Shakurov                                |

| Software Engineering Education                                                                                 |

| Educational Tests in "Programming" Academic Subject Development<br>O. Maksimenkova, V. Podbelskiy              |

| Automata Theory                                                                                                |

| The Parallel Composition of Timed Finite State Machines      O. Kondratyeva, M. Gromov                         |

| Separating Non-Deterministic Finite State Machines with Time-outs<br><i>R. Galimullin, N. Shabaldina</i>       |

| Testing of Software and Hardware Systems                                                                       |

| Model Based Conformance Testing for Extensible Internet Protocols<br>N. Pakulin, A. Tugaenko                   |

| Developing Test Systems for Multi-Modules Hardware Designs<br><i>M. Chupilko</i>                               |

| Application-Specific Methods and Tools                                                                         |

| Programming for Modular Reconfigurable Robots<br>A.Gorbenko, V. Popov                                          |

| Towards a Real-Time Simulation Environment on the Edge of Current Trends         E.Chemeritskiy, K. Savenkov.  |

| Computer Graphics and Vision                                                                                   |

| The Problem of Placement of Visual Landmarks      A. Gorbenko, M. Mornev, V Popov                              |

| Hand Recognition in Live-Streaming Video<br><i>M. Belov.</i>                                                   |

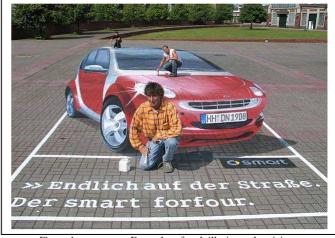

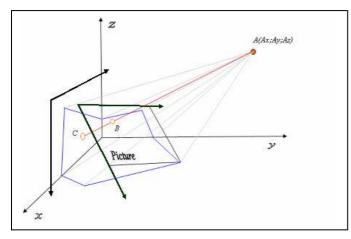

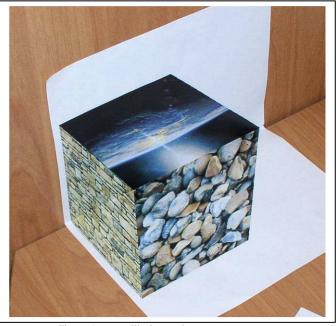

| 3D-Illusion Constructor      M. Rovkin, E. Yel'chugin, M. Filatova                                             |

## Foreword

Dear participants, we are glad to welcome you on the 5<sup>th</sup> Spring/Summer Young Researchers' Colloquium on Software Engineering (SYRCoSE). This year we have the pleasure of holding SYRCoSE in Yekaterinburg, the main industrial and cultural center of the Urals Federal District. The colloquium is hosted by the Ural State University (USU), one of the most prestigious universities in Russia. The event is organized by Institute for System Programming of RAS (ISPRAS) and Saint-Petersburg State University (SPSU) jointly with USU and SKB Kontur.

Program Committee has selected 24 papers that cover different topics of software engineering and computer science. Each submitted paper has been reviewed independently by two or three referees. Participants of SYRCoSE 2011 represent well-known universities, research institutes and IT companies such as Institute of Informatics Problems of RAS (IPI RAN), Intel, ISPRAS, MCST, Moscow State University, National Research Nuclear University "MEPhI", State University – Higher School of Economics, Tomsk State University, USU and Yaroslavl Demidov State University.

We would like to thank all the participants of SYRCoSE 2011 and their advisors for interesting papers. We are also very grateful to the PC members and the external reviewers for their hard work on reviewing the papers and selecting the program. Our thanks go to the invited speakers, Petr Skobelev (SEC "Knowledge Genesis") and Shihong Huang (Florida Atlantic University). We would also like to thank our sponsors, Russian Foundation for Basic Research (grant 11-07-06013- $\Gamma$ ) and Microsoft Research. Finally, our special thanks to Irina Voychitskaya (SKB Kontur), Maria Rudnichenko (SKB Kontur) and Tatyana Perevalova (USU) for their invaluable help in organizing the colloquium in Yekaterinburg.

Sincerely yours

Alexander Kamkin, Alexander Petrenko, Andrey Terekhov May 2011

## Committees

### **Program Committee Chairs**

Alexander K. Petrenko – Russia Institute for System Programming of RAS

### **Program Committee**

Habib Abdulrab - France National Institute of Applied Sciences, INSA-Rouen Sergey M. Avdoshin - Russia Higher School of Economics Eduard A. Babkin – Russia Higher School of Economics Victor P. Gergel – Russia Lobachevsky State University of Nizhny Novgorod Efim M. Grinkrug - Russia Higher School of Economics Maxim L. Gromov - Russia Tomsk State University Vladimir I. Hahanov – Ukraine Kharkov National University of Radioelectronics Vsevolod P. Kotlyarov - Russia Saint-Petersburg State Polytechnic University

- Oleg R. Kozyrev Russia Higher School of Economics

- Alexander A. Letichevsky Ukraine Glushkov Institute of Cybernetics, NAS

- Yury S. Lukach Russia Ural State University

- Tiziana Margaria Germany University of Potsdam

## **Organizing Committee Chairs**

Alexander S. Kamkin – Russia Institute for System Programming of RAS

## **Organizing Committee**

Yury S. Lukach – Russia Ural State University

Tatyana V. Perevalova Ural State University

| Andrey N. Terekhov – Russia<br>Saint-Petersburg State University                                    |

|-----------------------------------------------------------------------------------------------------|

|                                                                                                     |

| Igor V. Mashechkin – Russia<br>Moscow State University                                              |

| Alexander S. Mikhaylov – Russia<br>National Research Nuclear University "MEPHI"                     |

| Valery A. Nepomniaschy – Russia<br>Ershov Institute of Informatics Systems                          |

| Ivan I. Piletski – Belorussia<br>Belarusian State University of Informatics and<br>Radioelectronics |

| Vladimir Yu. Popov – Russia<br><sup>Ural State University</sup>                                     |

| Ruslan L. Smelyansky – Russia<br>Moscow State University                                            |

| Valeriy A. Sokolov – Russia<br>Yaroslavl Demidov State University                                   |

| Vladimir V. Voevodin – Russia<br>Research Computing Center of Moscow State University               |

| Mikhail V. Volkov – Russia<br><sup>Ural State University</sup>                                      |

| Rostislav E. Yavorsky – Russia<br>Microsoft                                                         |

| Nina V. Yevtushenko – Russia<br><sup>Tomsk</sup> State University                                   |

| Vladimir A. Zakharov – Russia<br>Moscow State University                                            |

| Irina A. Voychitskaya<br>SKB Kontur                                                                 |

| <br>                                                                                                |

Maria A. Rudnichenko

Mikhail V. Volkov

Ural State University

SKB Kontur

## Referees

Vladimir BASHKIN Victor GERGEL Efim GRINKRUG Maxim GROMOV Vladimir HAHANOV Alexander KAMKIN Vsevolod KOTLYAROV Victor KULIAMIN Natalia KUSHIK Egor KUZMIN Alexander LETICHEVSKY Tiziana MARGARIA Artem MELENTYEV Alexander MIKHAYLOV Valery NEPOMNIASCHY Dmitry PAVLENKO Alexander PETRENKO Ivan PILETSKI Vladimir POPOV Svetlana PROKOPENKO Alexey PROMSKY Alexey PROMSKY Natalia SHABALDINA Valery SOKOLOV Maria VETROVA Maria VETROVA Mikhail VOLKOV Rostislav YAVORSKY Nina YEVTUSHENKO

# Crowdsourcing Projects for Research, Education and Better Life

Extended abstract

Rostislav E. Yavorskiy Vice President, Models and Algorithms Witology, <u>http://witology.com</u> Office 215, Building 3, Kapranova Per. Moscow, 123242, Russia

*Abstract.* This paper provides a brief introduction into two open source projects in the area of Computer Science and Software Engineering in Russia

Crowdsourcing, open source projects, software engineering education, computer science, DOM API testing, wild fires monitoring

#### I. INTRODUCTION

According to Wikipedia [1] "Crowdsourcing is the act of outsourcing tasks, traditionally performed by an employee or contractor, to an undefined, large group of people or community (a "crowd"), through an open call." This paper describes two initiatives of this format, where a wide community of students and young researchers has been invited to participate in solving a big and important problem. The both projects are still active, so another goal of this paper is to attract new activists to join.

## II. DOM API TESTING FOR CONFORMANCE TO W3C STANDARD

Document Object Model Application Programming Interface (DOM API) standard specifies an interface for accessing and manipulating documents programmatically in Web browsers, see [2]. W3C group provides conformance tests for DOM API; statistics on test case numbers is presented in [5], see table 3. We just mention here that the standard specifies 946 methods and attributes, and some modules are not covered by the test suite at all.

A very rough estimate shows that deep and detailed analysis and test development for a DOM element may require up to one working week, so development of a full test suite would require approximately 20 men-years.

The goal of our project is to involve wide community into the work of creating the complete test suite, see [3].

#### A. Research

Creating test suites with a good coverage metrics is a challenging research task. One may start with [4-5] and then follow the references.

## The work described in this paper is partially sponsored by Microsoft Rus and Microsoft Research

#### B. Education

This project could be used as a good topic for course paper, diploma or even PhD thesis by students of Computer Science and Software Engineering departments of universities.

#### C. Better life

Taking into account the role of Internet in our life, there is no need to say much on justifying the importance of robustness and interoperability of Web browsers.

## III. USING SATTELITE IMAGES FOR MONITORING OF WILD FIRES

Wild fire is a regular phenomenon, which causes extensive damage both to property and human life. Satellite images provide a good tool for studying, analyzing, and predicting wild fires. A huge amount of satellite data is available online, see e.g. MODIS page [6].

Our project [7] is aimed at involving wide community of students and researchers into the work of analyzing the satellite images and developing tools and algorithms for better monitoring and predicting wild fires.

#### A. Research

There are four rather independent research areas, related to this project.

- *Scientific Databases.* See e.g. project on "Environmental Scenario Search Engine" [8].

- *Image Recognition*. See Open CV project for more [9-10].

- Scientific Data Management and Visualization. See e.g. Scientific Data Set project [11].

- *Domain specific research*. For example, models and critical factors for wild fires appearance and spreading.

#### B. Education

Similarly, this project provides numerous interesting examples to be used at the relevant courses in universities.

#### C. Better life

The importance of this project is obvious.

#### REFERENCES

- [1] Wikipedia, The Free Encyclopedia, Crowdsourcing http://en.wikipedia.org/wiki/Crowdsourcing

- [2] Document Object Model, <u>http://www.w3.org/DOM/</u>

- [3] DOM API Testing for conformance against W3C standard, http://domapitesting.codeplex.com

- [4] DOM API Contracts and Test Suite Development Using Code Contracts and Pex. Research Report. Institute for System Programming, Russian Academy of Sciences (ISP RAS) by order of Microsoft Research, November 2009. See <u>http://domapitesting.codeplex.com/documentation</u>

- [5] Test Development for DOM Support in Internet Browsers. Research report. Institute for System Programming, Russian Academy of Sciences

(ISP RAS) by order of Microsoft Research, June 2010. See http://domapitesting.codeplex.com/documentation

- [6] MODIS, Moderate Resolution Imaging Spectroradiometer, http://modis.gsfc.nasa.gov/

- [7] Monitoring of Wild Fires Project (in Russian) <u>http://gis-lab.info/projects/fires.html</u>

- [8] Open-source project Environmental Scenario Search Engine, http://esse.wdcb.ru/

- [9] И. Лысенков, Распознавание сгоревших территорий с помощью деревьев решений и OpenCV, <u>http://gis-lab.info/qa/burnedarea-opencv.html</u>

- [10] Open Source Computer Vision library, http://opencv.willowgarage.com/wiki/

- [11] SDS: Scientific DataSet library and tools, http://sds.codeplex.com/

The work described in this paper is partially sponsored by Microsoft Rus and Microsoft Research

## tRNA Computing Units and Programming Languages

Natalya Odincova Department of Mathematics and Mechanics Ural State University Ekaterinburg, Russia, 620083 Email: odincova.antalya@gmail.com

*Abstract*—In this paper we consider some new computing units for DNA-based computers. Construction of such unit essentially based on properties of tRNA. Therefore, we call them as tRNA computing units.

#### I. INTRODUCTION

In the recent years several new ideas have been developed to use non electronic natural phenomena for real, efficient computation. In classical electronic-based computations the information is stored and modified bitwise by electric and electromagnetic means. It is typical for this kind of computations that the number of steps performed per time unit is huge but the number of processors running in parallel is small. The main objective for the new approaches mentioned above is not to speed up the number of steps per time unit but to increase the degree of parallelism considerably. In 1985 D. Deutsch [1] proposed computers using quantumphysical effects to store and modify information. The quasiprobabilistic physical effect of quantum parallelism and mutual dependences of between all bits (coherence effects) allow to construct quantum algorithms that solve certain problems faster than any known probabilistic algorithm. In [1] Quantum Turing Machines are introduced as a theoretical model of such a kind of computation. In [2] quantum machine algorithms for the discrete logarithm and for integer factoring are given which run in polynomial time. In 1994 different approaches came up that used biological properties of DNA strings to store and modify information. The general idea is to use a large number of DNA strings as processors which compute in parallel. In [3] P. Pudlák introduced Genetic Turing Machines that are probabilistic machines which can simulate the evolution of a population of strings using two special operators controlling the inheritance and the survival of strings. In this model on each of the randomly chosen paths one string is processed. Also in 1994, L. Adleman [4] used biological experiments with DNA strings to solve some particular instances of the directed hamiltonian path problem which is considered to be intractable because of its NP-completeness. In [5] – [7] R. Lipton showed how to extend this idea to solve any problem and discussed the practical relevance of this approach. He defined a model of biological computing that has, besides the

Vladimir Popov Department of Mathematics and Mechanics Ural State University Ekaterinburg, Russia, 620083 Email: Vladimir.Popov@usu.ru

classical means, the ability of manipulating large collections of DNA strings. Performing one of the special operations on a test tube means some simple manipulation of each of the strings in the test tube. In that way each DNA string corresponds to a piece of information, and all these pieces can be modified in parallel. At current DNA manipulation technology levels, DNA computing provides no advantage over electronic computers, for example, when encoding the computing task with DNA molecule in Adlemans directed hamiltonian path problem, if the n is equal to 100, the amount of DNA required would be larger than the weight of the earth. There is not enough room for improvement on algorithm to make the number of DNA molecules practically small. At this stage, some people began to worry about the directions of DNA computing study. However, in other sub-fields of DNA computing, great progress has been made. There are currently several research disciplines driving towards the creation and use of DNA nanostructures for both biological and nonbiological applications. These converging areas are:

- the miniaturization of biosensors and biochips into the nanometer scale regime;

- the fabrication of nano-scale objects that can be placed in intracellular locations for monitoring and modifying cell function;

- the replacement of silicon devices with nano-scale molecular-based computational systems, and the application of biopolymers in the formation of novel nanostructured materials with unique optical and selective transport properties.

DNA computing employs DNA molecule as a main resource to fulfill computing tasks. However, the concept of primary DNA computing unit keeps obscure. It is recently realized that there are multiple forms of basic DNA computing units. Adleman uses short oligonucleotides to encode mathematical problems. The computing process is mainly performed in the form of hybridization. Ligation and other molecular manipulation steps are used for output abstraction. The correct answer is hidden in a vast amount of different hybridization results. Rothemund proposed a Turing machinelike DNA computing unit [8]. In [9] – [11] published another study in which an autonomous programmable DNA automaton is created. In particular, in [9] - [11] for DNA automaton used a doublestranded DNA as input, endonuclease and DNA ligase as main hardware, transition molecules as software, thus creating a two-state molecular finite automaton with a two-symbol input, eight transition rules and 765 syntactically distinct programs. DNA self-assembly has become one of the most important directions for DNA computing [12] - [19]. Because of its universal computing capability, DNA assembly provides another avenue for universal DNA computer development. DNA computing by self-assembly is basically a tiling process, and the tile types can vary a lot. The tiles can be formed with several singlestranded oligos, and each tile can have different sticky DNA ends for a number of combinations with other same or different tiles. The tiling can be designed in a twodimensional or three-dimensional way, and the scale for tiling should also be able to control. DNA assembly can be completely programmed, though molecular biology experiments are still a bottle-neck for large scale assembly. In [19] authors brought a new landscape for this avenue. Combinatorial cellular automata also used in designing any tiling shapes. Besides, the natural affinity of DNA to bind with proteins, some types of small molecules, even metal atoms, makes it possible that assembled DNA can work as an inherent or transient matrix for novel computing devices. In [20] - [23]published a study in ribozyme unit research area. Ribozyme is a piece of nucleic acid fragment with unique three-dimensional structure that has an enzymatic ability to cut specific complementary oligos as substrate. If another oligo binds with the ribozyme and prevents it from forming enzymatic conformation, the ribozyme stays in an inactive form. In [20] - [23]founded ribozymes that can be easily manipulated as logical gates. Thus such ribozyme can mimic conventional electronic computing devices and theoretically develop universal DNA computing system. Ribozymes can work as automaton, though for the time being ribozyme or deoxyribozyme automaton is still in its infancy. Ribozymebased DNA computing unit may be extremely useful in designing logical computing devices in the future, for example, single-molecule logical gate. In [24], [25] also trying to employ ribozyme-based DNA computing as a potential vehicle for in vivo DNA computing. Instead of making ribozymes into logical gates or automata, in [24], [25] ribozymes used to build simple automata that may be easier for in vivo usage. Membrane computing [26], [27] can be regarded as a unique biological computing system. A cell is the basic unit for membrane computing system. This unit is not a DNA computing unit. However, membrane system provides another sort of self-assembly tile, and each such unit can hold DNA in it and may be able to translocate DNA molecules between each unit in the future, so we would like to treat such unit as a special DNA computing unit. It might be also called cell computing, a natural distributed architecture of a computing unit where any other DNA computing unit processes might be embedded. Since no kind of artificial membrane computing systems has been tested in the form of biochemical or physical biochemical experiments, it is likely that the natural cells may

be firstly tried by cell molecular biology manipulations. So some *in vivo* DNA computing technology may be needed to develop beforehand.

In this paper we consider some new DNA computing units. Construction of such unit essentially based on properties of tRNA. Therefore, we call them as tRNA computing units.

#### II. tRNA COMPUTING UNITS

Transfer RNA (tRNA) is RNA that transfers a specific active amino acid to a growing polypeptide chain at the ribosomal site of protein synthesis during translation. tRNA has a 3'terminal site for amino acid attachment. This covalent linkage is catalyzed by an aminoacyl tRNA synthetase. It also contains a three base region called the anticodon that can base pair to the corresponding three base codon region on mRNA. Each type of tRNA molecule can be attached to only one type of amino acid, but because the genetic code contains multiple codons that specify the same amino acid, tRNA molecules bearing different anticodons may also carry the same amino acid. An anticodon [28] is a unit made up of three nucleotides that correspond to the three bases of the codon on the mRNA. Each tRNA contains a specific anticodon triplet sequence that can base-pair to one or more codons for an amino acid. To provide a one-to-one correspondence between tRNA molecules and codons that specify amino acids, 61 types of tRNA molecules would be required per cell. However, many cells contain fewer than 61 types of tRNAs because the wobble base is capable of binding to several, though not necessarily all, of the codons that specify a particular amino acid. A minimum of 31 tRNA are required to translate, unambiguously, all 61 sense codons of the standard genetic code [29].

The main function of tRNA is to recognize a fragment of single-stranded DNA molecule which consists of three nucleotides. As a result of such action is established a correspondence between the triplet of nucleotides of DNA nucleotides and a triple contact element of the tRNA molecule. In vivo tRNA molecule used for the amino acids synthesis. However, at least *in vitro* using special enzymes, we can stop the natural process of protein synthesis at the stage of reading nucleotide triplets of the DNA molecule and start the process of reading information from the tRNA molecules. As a result, we obtain a new DNA molecule. In the classical model of tRNA function we do not get anything interesting. In view of one-to-one correspondence between triples of DNA and tRNA we simply obtain a copy or some subsequence of the original DNA molecule. More precisely, in vitro we can produce any of following operations. Let

$$F[P](x) = y$$

where F[P](x) is a function with a parameter P of the variable x defined as follows:

$$x = x[1]z[1]x[2]z[2] \dots x[n]z[n]x[n+1],$$

$$y = z[1]z[2] \dots z[n],$$

$$\begin{split} & z[i] \in P \subseteq \mathcal{P} = \{UUU, UUC, UUA, \\ & UUG, UCU, UCC, UCA, UCG, \\ & UAU, UAC, UGU, UGC, UGG, \\ & CUU, CUC, CUA, CUG, CCU, \\ & CCC, CCA, CCG, CAU, CAC, \\ & CAA, CAG, CGU, CGC, CGA, \\ & CGG, AUU, AUC, AUA, AUG, \\ & ACU, ACC, ACA, ACG, AAU, \\ & AAC, AAA, AAG, AGU, AGC, \\ & AGA, AGG, GUU, GUC, GUA, \\ & GUG, GCU, GCC, GCA, GCG, \\ & GAU, GAC, GAA, GAG, GGU, \\ & GGC, GGA, GGG\}^+, \\ & 1 \leq i \leq n, \\ & x[j] \in \{A, U, C, G\}^*, \\ & 1 \leq j \leq n+1. \end{split}$$

Note that *in vitro* the length of each word x[j] depends on the specific experimental conditions and the presence in this words subwords from

$$\{UAA, UGA, UAG\}.$$

In general case we can suppose that the length of x[j] is an arbitrary number. In vivo

$$x[j] \in \{UAA, UGA, UAG\}^*$$

.

So, we obtain some set of tRNA computing units each of which is given by some operation F[P](x). We call them as classical tRNA computing units.

Complete sets of tRNAs from one organism, including at least one isoacceptor species for each of the twenty amino acids, are known for several eubacteria (Mycoplasma capricolum, Bacillus subtilis, Escherichia coli), yeast (Saccharomyces cerevisiae) and chloroplasts (Euglena gracilis, Marchantia polymorpha, Nicotiana tabacum) or mitochondria (Torulopsis glabra, ratus ratus). The number of genes for a particular isoaccepting tRNA varies depending on the organism. Although these genes might have the same primary structure, it is more common that isoacceptor tRNAs feature the same anticodon but slightly differing sequences. In yeast, for example, the two tRNA<sup>*phe*</sup><sub>*GAA*</sub> [31] and the two tRNA<sup>*thr*</sup><sub>*IGU*</sub> [32] are identical except two nucleotides. Compensatory mutations frequently occur in the case when the difference between two isoacceptors is located in a stem. Again in yeast tRNA<sup>phe</sup>, an A-U base pair in the amino acid acceptor stem is exchanged for a G-C pair. The same replacement is found in yeast tRNA.

Transfer RNA is the most extensively modified nucleic acid in the cell. Modified nucleotides are contained in tRNAs from all three phylogenetic domains (archaea, bacteria, eucarya [33], [34]). The modifications are not introduced during transcription, but are formed after the synthesis of the polynucleotide chain, serving for an improvement of the specificity and efficiency of tRNA biological functions. To date, more than eighty modified residues have been discovered and their chemical structures revealed [35]. Modified nucleotides are located at 61 different positions in tRNAs, mainly in loop regions. A large variety is present in the anticodon area, especially in the first position of the anticodon (position 34), and one base 3' to the anticodon (position 37). Apart from one exception (archaeosine at position 15 in archael tRNAs [36], all hypermodified residues are found in this region. Minor modifications like methylated or thiolated derivatives are usually situated outside the anticodon, with only one or two kinds of modified nucleotides present at each position. Some are common to almost all species, such as Dihydrouridine in D loops and Ribothymine in T loops, whereas others are characteristic of specific tRNAs. Examples are found in the hypermodified wybutosine residue (a guanosine derivative) at position 37 in almost all eukaryotic tRNA<sup>phe</sup> (except that from Bombyx mori and Drosophila melanogaster) and queueosine (another complicated post-transcriptional modification of guanosine) at the first anticodon position of certain tRNAs specific for tyr, his, asn and asp from eubacteria and eukaryotes. In both domains, modification takes place at different stages during the processing of precursor tRNA, depending strongly on the concentration of the substrate as well as on both the amount and the activity of tRNA-modifying enzymes. Several studies have been carried out on precursor tRNA<sup>tyr</sup>. The biosynthesis in Xenopus laevis oocytes initiated by injection of the yeast tRNA<sup>tyr</sup> gene into either the nucles or the cytoplasma revealed that most base modifications occur in a sequential fashion in the nucleus before splicing [37], [38].

In many cases, the third nucleotide of the contact element of mutant tRNA is not functional. Non-functionality of third nucleotide of the contact element is connected with various mutations that lead to changes in the secondary and the tertiary structures of tRNA. It should be noted that these changes are stable. Note also that these mutations are quite common. In particular, the synthesis of some vital proteins of *Homo Sapiens* is only possible with the assistance of some mutant tRNA. The classical transformation

$$XYZ \to XYZ$$

for some such mutant tRNAs can be represented in form

$$XY \rightarrow XYZ$$

in case when a third nucleotide of tRNA contact element does not functional for the original DNA and for some other tRNAs can be represented in form

#### $XYZ \to XY$

in case when a third nucleotide of tRNA contact element does not functional for the new DNA [30]. So, we obtain the

following set of relations:

$\mathcal{S} = \{UUU = UU,$ UUC = UU, UUA = UU, UUG = UU,UCU = UC, UCC = UC, UCA = UC,UCG = UC, UAU = UA, UAC = UA,UGU = UG, UGC = UG, UGG = UG,CUU = CU, CUC = CU, CUA = CU,CUG = CU, CCU = CC, CCC = CC,CCA = CC, CCG = CC, CAU = CA,CAC = CA, CAA = CA, CAG = CA,CGU = CG, CGC = CG, CGA = CG,CGG = CG, AUU = AU, AUC = AU,AUA = AU, AUG = AU, ACU = AC,ACC = AC, ACA = AC, ACG = AC,AAU = AA, AAC = AA, AAA = AA,AAG = AA, AGU = AG, AGC = AG,AGA = AG, AGG = AG, GUU = GU,GUC = GU, GUA = GU, GUG = GU,GCU = GC, GCC = GC, GCA = GC,GCG = GC, GAU = GA, GAC = GA,GAA = GA, GAG = GA, GGU = GG,GGC = GG, GGA = GG, GGG = GG

where

$$XYZ = XY$$

denotes the pair

$$XYZ \to XY,$$

$XY \to XYZ.$

We can produce any of following operations. Let

$$G[S, P](x) = y$$

where G[S, P](x) is a function with parameters S and P of the variable x defined as follows:

$$\begin{split} x &= x[1]x[2]\dots x[n],\\ y &= y[1]y[2]\dots y[n],\\ z, \, x[i] \to z \in S \subseteq \mathcal{S}\\ x[i], \, y[i] \in P \subseteq \mathcal{P}\\ \text{empty word} \end{split}$$

So, we obtain some set of tRNA computing units each of which is given by some operation G[S, P](x). We call them as mutational tRNA computing units.

The frequent occurence of non-canonical G-U base pairs [39] is a noticeable feature of stem regions. Since their first discovery in [40], other possible non-canonical pairs (for example A-A, C-C, C-U, G-A, U-U, U-Y) have been detected in the stems of various tRNAs [41]. G-U pairs, however, occur with the highest frequency. As to stems, a frequently occuring length can be attributed to loops as well. Anticodon and T loops contain seven nucleotides, whereas D loops and variable regions are areas of various lengths. An important discovery regarding the primary structure was made in the early 1970s. Certain positions in tRNAs are occupied by invariant or semi-invariant nucleotides.

Insights concerning characteristic behaviour of natural tRNA molecules were subsequently applied to the design of artificial tRNA molecules [30]. Using the complete sets of identity elements of some E. coli tRNAs as sequence constraints in inverse folding, a large amount of thermodynamically very stable sequences was obtained and subsequently sorted out due to inefficient folding behaviour.

Genes of interest can be selectively metallized via the incorporation of modified triphosphates [42]. These triphosphates bear functions that can be further derivatized with aldehyde groups via the use of click chemistry. Treatment of the aldehyde-labeled gene mixture with the Tollens reagent, followed by a development process, results in the selective metallization of the gene of interest in the presence of natural DNA strands.

In [43] reported a simple solution based method for the gold (Au) metallization of DNA resulting in a Au nanowire network. Advantage of solution based approach is that it allows the removal of excess gold  $(Au^{+3})$  ions by extraction with tetraoctylammonium bromide (TOAB) in order to avoid non specific metallization. Further it has been shown that Au metallized DNA obtained in aqueous phase can be transferred to organic phase using hexadecyl aniline (HDA). Au metallized DNA has potential application in nanoscale devices.

Also a number of small organic ribonucleases have been synthesized with rigid polycationic structures containing an aromatic framework with two residues of bis-quaternary salts of 1,4-diazabicyclo[2.2.2]octane (DABCO) bearing various substituents [44]. The compounds carrying positively charged groups connected via rigid linker are expected to bend the sugar-phosphate backbone and can stimulate the intramolecular phosphoester transfer reaction.

Since we can use artificial nucleotides and artificial tRNA molecules, we can consider artificial tRNA computing units. In this case we consider some alphabet  $\Sigma$  and the set of relations

$$\begin{split} \mathcal{Q} &= \{X_1Y_1Z_1 \rightarrow X_1Y_1Z_1, \\ &X_2Y_2 \rightarrow X_2Y_2Z_2, \\ &X_3Y_3Z_3 \rightarrow X_3Y_3 \mid \\ &X_i, Y_i, Z_i \in \Sigma, 1 \leq i \leq 3\}. \end{split}$$

We can define following operations. Let

$$H[Q](x) = y$$

where H[Q](x) is a function with a parameters Q of the variable x defined as follows:

$$\begin{aligned} x &= x[1]x[2]\dots x[n], \\ y &= y[1]y[2]\dots y[n], \\ y[i] &= \begin{cases} z, \, x[i] \to z \in Q \subseteq \mathcal{Q} \\ \\ \text{empty word} \end{cases} \end{aligned}$$

We obtain the set of tRNA computing units each of which is given by some operation H[Q](x). We call them as artificial tRNA computing units.

#### III. tRNA PROGRAMMING LANGUAGES

Let  $k \ge 0$  and  $m \ge 1$  be variables for natural numbers, let  $a, b \in \{0, 1\}$ , let x be a word variable and let T,  $T_1$  and  $T_2$  be set variables. Let  $I(x) \in \{0,1\}^*$  be the contents of the word variable x, and let  $I(T) \subseteq \{0,1\}^*$  be the contents of the set variable T in a given moment. We define the cut operation  $\setminus$  by  $\setminus av = v$  and  $\setminus \Delta = \Delta$  where  $\Delta$  is the empty word. Different types of DNA-computers use the following instructions with set operations and conditions with set tests [45].

$\mathbf{T}$

$$\begin{split} T &= T_1 \cup T_2, \\ I(T_1) \cup I(T_2); \\ T &= In(k), \\ &\{0,1\}^k; \\ T &= T_1 \cdot T_2, \\ I(T_1) \cdot I(T_2); \\ T &= \backslash T_1, \\ &\{ \backslash z \mid z \in I(T_1) \}; \\ T &= Sw(T_1), \\ &\{ y \mid \exists v \exists w (vyw \in I(T_1)) \}; \\ T &= a \cdot T_1, \\ &\{a\} \cdot I(T_1); \\ T &= Eq(T_1 \cdot m \cdot a), \\ &\{ vaw \mid (v0w \in I(T_1) \lor v1w \in I(T_1)) \land |v| = m - 1 \}; \end{split}$$

$$\begin{split} T &= Bs(T_1 \cdot m \cdot a \cdot b),\\ \{vaw \mid v0w \in I(T_1) \wedge |v| = m-1\} \cup\\ \{vbw \mid v1w \in I(T_1) \wedge |v| = m-1\}; \end{split}$$

$$T = Bx(T_1 \cdot m \cdot a),$$

$$I(T_1) \cap (\{0,1\}^{m-1}a\{0,1\}^*);$$

$$T = Br(T_1 \cdot m \cdot a \cdot x),$$

$$\{vI(x)w \mid vaw \in I(T_1) \land |v| = m - 1\};$$

$$T = Bl(T_1 \cdot m \cdot a \cdot b),$$

$$\{vbw \mid vaw \in I(T_1) \land |v| = m - 1\};$$

$$x \in T,$$

$$I(x) \in I(T);$$

$$T = \emptyset,$$

$$I(T) = \emptyset,$$

$$T_1 \subseteq T_2,$$

$$I(T_1) \subseteq I(T_2).$$

We can use our computing units independently or add them to this computing units. Depending on experimental conditions using the same computing units we can obtain essentially different programming languages. For example, if we allow unrestricted appliance of operations F[P](x) and G[S, P](x), then we can consider the following semigroup as a model of computations:

$$\langle A, U, C, G \mid \mathcal{S} \rangle.$$

Note that

$$UAA = UACA = UAC = UA,$$

$UGA = UGGA = UGG = UG,$

$UAG = UACG = UAC = UA.$

Therefore,

$$\begin{split} \langle A, U, C, G \mid \mathcal{S} \rangle &= \\ \{U, A, C, G, \\ UU, UA, UC, UG, \\ AU, AA, AC, AG, \\ CU, CA, CC, CG, \\ GU, GA, GC, GG \}. \end{split}$$

From other hand, using restricted appliance of operations F[P](x) and G[S, P](x), we can easily obtain a semigroup with undecidable word problem.

Note that for tRNA programming languages we have only set and string variables and constants. This is a characteristic feature of all programming languages for DNA computing. In the case of DNA computing, we have significant difficulties with numerical operations and numbers themselves. But "difficult" does not mean "impossible". For example, suppose that we have a binary register

#### $a_1 a_2 a_3 a_4$

where  $a_1, a_2, a_3, a_4 \in \{0, 1\}$ . Assume that we want to define some bit operations. We can emulate this binary register the following word:

$$GGA_1GGA_2GGA_3GGA_4$$

where

$$A_i = \begin{cases} G, a_i = 0 \\ \\ C, a_i = 1 \end{cases}$$

$G_{0,1,1}[S_1, P] : GGCx[1]x[2]x[3] \to GGx[1]x[2]x[3],$  $G_{0,1,2}[S_2, P]: GGx[1]x[2]x[3] \to GGGx[1]x[2]x[3],$  $G_{0,2,1}[S_1, P] : x[1]GGCx[2]x[3] \to x[1]GGx[2]x[3],$  $G_{0,2,2}[S_2, P]: x[1]GGx[2]x[3] \to x[1]GGGx[2]x[3],$  $G_{0,3,1}[S_1, P]: x[1]x[2]GGCx[3] \to x[1]x[2]GGx[3],$  $G_{0,3,2}[S_2, P]: x[1]x[2]GGx[3] \rightarrow x[1]x[2]GGGx[3],$  $G_{0,4,1}[S_1, P] : x[1]x[2]x[3]GGC \to x[1]x[2]x[3]GG,$  $G_{0,4,2}[S_2, P]: x[1]x[2]x[3]GG \rightarrow x[1]x[2]x[3]GGG,$  $G_{1,1,1}[S_3, P] : GGGx[1]x[2]x[3] \to GGx[1]x[2]x[3],$  $G_{1,1,2}[S_4, P]: GGx[1]x[2]x[3] \to GGCx[1]x[2]x[3],$  $G_{1,2,1}[S_3, P]: x[1]GGGx[2]x[3] \to x[1]GGx[2]x[3],$  $G_{1,2,2}[S_4, P]: x[1]GGx[2]x[3] \to x[1]GGCx[2]x[3],$  $G_{1,3,1}[S_3, P]: x[1]x[2]GGGx[3] \to x[1]x[2]GGx[3],$  $G_{1,3,2}[S_4, P]: x[1]x[2]GGx[3] \to x[1]x[2]GGCx[3],$  $G_{1,4,1}[S_3, P]: x[1]x[2]x[3]GGG \to x[1]x[2]x[3]GG,$  $G_{1,4,2}[S_4, P]: x[1]x[2]x[3]GG \to x[1]x[2]x[3]GGC,$  $x[i] \in P = \{GGG, GGC\},\$  $S_1 = \{GGC \to GG\}, S_2 = \{GG \to GGG\},\$  $S_3 = \{GGG \to GG\}, S_4 = \{GG \to GGC\}.$

Let

$$B_{i,j}(x) \rightleftharpoons G_{i,j,2}(G_{i,j,1}(x)).$$

It is easy to check that using  $B_{i,j}$  we can obtain arbitrary bit operations.

#### **IV. CONCLUSION**

In this paper we consider some new computing units which can be used in different programming languages for DNAbased computers.

As the main direction of further research we can mention the rigorous formalization and classification of programming languages based on tRNA computing units and the study of computational power of such programming languages.

#### ACKNOWLEDGMENT

The work was partially supported by Grant of President of the Russian Federation MD-1687.2008.9 and Analytical Departmental Program "Developing the scientific potential of high school" 2.1.1/1775.

#### REFERENCES

- D. Deutsch. Quantum theory, the Church-Turing principle and the universal quantum computer, Proceedings of the Royal Society London, 1985, Vol. A400, 97–117.

- [2] P. W. Shor. Algorithms for quantum computation: Discrete logarithms and factoring, Proceedings of the 35th IEEE Symposium on Foundations of Computer Science, 1994. pp.124–134.

- [3] P. Pudlák. Complexity theory and genetics, Proceedings of 9th Conference on Structure in Complexity Theory, 1994. pp.183–195.

- [4] L. M. Adleman. Molecular computation of solutions to combinatorial problems, Science, 1994, Vol. 266, 1021–1024.

- [5] R. J. Lipton. Speeding up computations via molecular biology, Technical report, Princeton University, 1994.

- [6] R. J. Lipton. Using DNA to solve NP-complete problems, Technical report, Princeton University, 1995.

- [7] R. J. Lipton. DNA solution of hard computational problem, Science, 1995, Vol. 268, 542–545.

- [8] P. W. K. Rothemund. A DNA and restriction enzyme implementation of Turing machines, R.J.Lipton and E.B.Baum, editors. DNA Based Computers: Proceedings of the DIMACS Workshop, Princeton University, Providence, Rhode Island, 1996. pp.75–119.

- [9] Y. Benenson, T. Paz-Elizur, R. Adar, E. Keinan, Z. Livneh, E. Shapiro. Programmable and autonomous computing machine made of biomolecules, Nature, 2001, Vol. 414, 430–434.

- [10] Y. Benenson, R. Adar, T. Paz-Elizur, E. Keinan, Z. Livneh, E. Shapiro. DNA molecule provides a computing machine with both data and fuel, Proceedings of the National Academy of Sciences of the United States of America, 2003, Vol. 100, 2191–2196.

- [11] Y. Benenson, B. Gil, U. Ben-Dor, R. Adar, E. Shapiro. An autonomous molecular computer for logical control of gene expression, Nature, 2004, Vol. 429, 423–442.

- [12] T. H. LaBen, H. Yan, J. Kopatsch, F. Liu, E. Winfree, J. H. Reif, N. C. Seeman. *The Construction of DNA Triple Crossover Molecules*, Journal of the American Chemical Society, 2000, Vol. 122, 1848–1860.

- [13] H. Li, S. H. Park, J. H. Reif, T. H. LaBean, H. Yan. DNA-Templated Self-Assembly of Protein and Nanoparticle Linear Arrays, Journal of American Chemistry Society, 2004, Vol. 126, 418–419.

- [14] S. H. Park, H. Yan, J. H. Reif, T. H. LaBean, G. Finkelstein. *Electronic nanostructures templated on self-assembled DNA scaffolds*, Nanotechnology, 2004, Vol. 15, 525–527.

- [15] N. C. Seeman. Nucleic Acid Junctions and Lattices, Journal of Theoretical Biology, 1982, Vol. 99, 237–247.

- [16] A. T. Winfree. *The Geometry of Biological Time*, Springer-Verlag, Berlin, 2000.

- [17] H. Yan, T. H. LaBean, L. Feng, J. H. Reif. Directed Nucleation Assembly of Barcode Patterned DNA Lattices, Proceedings of the National Academy of Science of the United States of America, 2003, Vol. 100, 8103–8108.

- [18] H. Yan, S. H. Park, G. Finkelstein, J. H. Reif, T. H. LaBean. DNA-Templated Self-Assembly of Protein Arrays and Highly Conductive Nanowires, Science, 2003, Vol. 301, 1882–1884.

- [19] P. Yin, A. J. Turberfield, J. H. Reif. Design of an Autonomous DNA Nanomechanical Device Capable of Universal Computation and Universal Translational Motion, Tenth International Meeting on DNA Based Computers. LNCS 3384, Springer-Verlag, New York, 2005. pp.426–444.

- [20] M. N. Stojanovic, T. H. E. Mitchel, D. Stefanovic. *Deoxyribozyme-based Logic Gates*, Journal of American Chemistry Society, 2002, Vol. 124, 3555–3561.

- [21] M. N. Stojanovic, P. de Prada, D. W. Landry. *Homogeneous assays based on deoxyribozyme catalysis*, Nucleic Acids Reserch, 2000, Vol. 28, 2915.

- [22] M. N. Stojanovic, D. Stefanovic. A deoxyribozyme-based Molecular Automaton, Nature Biotechnology, 2003, Vol. 21, 1069.

- [23] M. N. Stojanovic, D. Stefanovic. Deoxyribozyme-based Half-Adder, Journal of American Chemistry Society, 2003, Vol. 125, 6673.

- [24] http://bdcc.kmip.net/htmls/dnacomputer/index.php

- [25] http://bi.snu.ac.kr/biocomputers2004

- [26] G. Păun. Membrane Computing: An Introduction, Springer-Verlag, Berlin, 2002.

- [27] G. Păun. Membrane computing: Main ideas, basic results, applications, Molecular Computational Models: Unconventional Approaches (M. Gheorghe, ed.), Idea Group Publ., London, 2004. pp.1–31.

- [28] G. Felsenfeld, G. Cantoni. Use of thermal denaturation studies to investigate the base sequence of yeast serine sRNA, Proceedings of the National Academy of Science of the United States of America, 1964, Vol. 51, 818–826.

- [29] H. Lodish, A. Berk, P. Matsudaira, C. A. Kaiser, M. Krieger, M. P. Scott, S. L. Zipursky, J. Darnell. *Molecular Biology of the Cell*, W.H. Freeman, New York, 2004.

- [30] M. D. Friede. Design of artificial tRNAs, Dissertation zur Erlangung des akademischen Grades Doctor rerum naturalium, Vorgelegt der Formalund Naturwissenschaftlichen Fakultät der Universität Wien, Wien, 2001.

- [31] G. Keith and G. Dirheimer. Evidence for the existence of an expressed minor variant tRNAphe in yeast, Biochemical and Biophysical Research Communications, 142:183–187, 1987.

- [32] J. Weissenbach, I. Kiraly, and G. Dirheimer. Primary structure of tRNAthr 1a and b from brewer's yeast, Biochimie, 59:381–391, 1977.

- [33] M. Sprinzl, C. Horn, M. Brown, A. Ioudovitch, and S. Steinberg. Compilation of tRNA sequences and sequences of tRNA genes, Nucleic Acids Research, 26:148–153, 1998.

- [34] C. R. Woese, O. Kandler, and M. L. Wheelis. Towards a natural system of organisms: proposal for the domains archaea, bacteria and eucarya, Proceedings of the National Academy of Sciences of the United States of America, 87:4576–4579, 1990.

- [35] G. R. Bjork, J. M. Durand, T. G. Hagervall, R. Leipuviene, H. K. Lundgren, K. Nilsson, P. Chen, Q. Qian, and J. Urbonavicius. *Transfer RNA* modification: in on translational frameshifting and metabolism, FEBS Letters, 452:47–51, 1999.

- [36] C. G. Edmonds, P. F. Crain, R. Gupta, T. Hashizume, C. H. Hocart, J. A. Kowalak, S. C. Pomerantz, K. O. Stetter, and J. A. McCloskey. *Post-transcriptional modification of tRNA in thermophilic archae (archeabac-teria)*, Journal of Bacteriology, 173:3138–3148, 1991.

- [37] D. A. Melton, E. M. de Robertis, and R. Cortese. Order and intracellular location of the events involved in the maturation of a spliced tRNA, Nature, 284:143–148, 1980.

- [38] K. Nishikura and E. M. De Robertis. RNA processing in microinjected xenopus oocytes. Sequential addition of base modifications in the spliced transfer RNA, Journal of Molecular Biology, 145:405–420, 1981.

- [39] B. Masquida and E. Westhof. On the wobble G-U and related pairs, RNA, 6:9–15, 2000.

- [40] R. W. Holley. Structure of an alanine transfer ribonucleic acid, JAMA, 194:868–871, 1965.

- [41] N. B. Leontis and E. Westhof. Conserved geometrical base-pairing patterns in RNA, Quarterly Review of Biophysics, 31:399–455, 1998.

- [42] G. A. Burley, J. Gierlich, M. R. Mofid, H. Nir, S. Tal, Y. Eichen, and T. Carell. *Directed DNA Metallization*, Journal of the American Chemical Society, 128(5):1398–1399, 2006.

- [43] A. S. Swami, N. Brun, and D. Langevin. *Phase Transfer of Gold Metallized DNA*, Journal of Cluster Science, 20(2):281–290, 2009.

- [44] E. A. Burakova and V. N. Silnikov. *Molecular Design of Artificial Ribonucleases Using Electrostatic Interaction*, Nucleosides, Nucleotides and Nucleic Acids, 23(6-7):915–920, 2004.

- [45] D. Rooß and K. W. Wagner. On the Power of DNA-Computing, Information and Computation, 131(2)95–109, 1996.

## Using Hardware-Assisted Virtualization to Protect Application Address Space Inside Untrusted Environment

Denis Silakov Institute for System Programming at the Russian Academy of Sciences Moscow, Russian Federation Email: silakov@ispras.ru

Abstract—In this paper we present a virtualization-based approach of protecting execution of trusted applications inside potentially compromised operating system. In out approach, we do not isolate application from other processes in any way; instead, we use hypervisor to control processes inside OS and to prevent undesired actions with application resources. The only requirement for our technique to work is presence of hardware support for virtualization; no modifications in application or OS are required.

Index Terms—Virtual Machine Monitor, Hypervisor, Security, Protection

#### I. INTRODUCTION

In modern software world, an operating system is a key component responsible for many security aspects of application execution process. In particular, it should provide possibilities to manage access permissions of application files and other resources, guarantee isolation of application address space in memory and so on.

However, many widespread operating systems (such as Linux or Windows) are known to be subjected to vulnerabilities which can be used by malicious code to compromise the whole system or particular application. As operating systems evolves, vulnerabilities are detected and fixed. But at the same time a lot of new features are added which potentially introduce new vulnerabilities. Size of code which is executed with highest privileges in modern OS is large. In particular, many popular systems are based on monolithic kernel where every device driver is a part of the kernel (that is, works in the same address space with other kernel parts and other drivers). It is common for drivers to contain issues. Vulnerability research performed in 2005 has shown that device drivers were responsible for about 85% of failures in Windows XP [1]; similar statistics was reported for Linux [2]. It is very likely that the situation will not change in the near future, since size of drivers grows faster than size of any other part of the kernel [3].

Microkernel-based operating systems are claimed to be more secure due to the fact that the size of code executed in privileged mode is very small [4]. However, in such systems interaction between micro kernel and drivers which becomes quite expensive. If used on a desktop machine with lots of peripheral devices, such systems often demonstrate worse performance. In addition, there are a lot of applications developed for widespread OSes with monolithic kernels. It would be very expensive to port all these programs to a system with completely new architecture. As a result, nowadays microkernel-based systems are primarily used either in highly tailored areas (e.g., QNX for embedded real-time systems) or for educational purposes (e.g., Minix).

Thus, there is a need for application protection techniques that will not require modifications of existing operating systems or applications, but at the same time will provide more reliable and secure services than traditional approaches.

One of the possible techniques is to use hardware-assisted virtualization. As implemented in modern Intel and AMD processors, it allows to launch a program (called *hypervisor*) that has full control over hardware and runs with higher privileges than OS. Normally, hypervisor is responsible for virtualization (e.g., creating and managing virtual machines), but its functionality can be enhanced. In particular, it can provide some security services. Hypervisor is usually much more smaller than OS (for example, most hypervisors do not have a large set of device drivers). As a result, hypervisor potentially contains less vulnerabilities and usually considered to be more secure than commodity operating systems. In this paper, we suggest an approach for protecting application address space using hypervisor.

The remainder of the paper is structured as follows: Section 2 observes existing virtualization-based approaches to protection of application resources. Section 3 describes general architecture of our protection system and specific aspects of protecting address space of applications of different kinds. Section 4 describes implementation of our approach and present performance measurement results. Finally, Section 5 summarizes the main ideas.

#### **II. HYPERVISOR-BASED PROTECTION SYSTEMS**

The idea of using hypervisor for different security tasks has got much attention after Intel and AMD introduced their first implementations of hardware-assisted virtualization in years 2005-2006. Many approaches requires modifications of applications, OS (e.g., [5] or [6]) or even hardware ([7], [8]). Though some of these approaches seem to be quite effective, their usage is rather limited.

A promising approach is Overshadow technology of memory protection suggested by researches from Stanford and Princeton Universities, MIT and VMware, Inc ([9]). It does not require modifications of OS or applications. Instead, it encrypts process memory area of working processes. If OS or other program try to access process memory, they only see encrypted data. For trusted process itself, a "normal" memory view is provided. Similar approach based on dynamic encryption of application memory is presented in [10].

However, these approaches are primarily aimed at hiding application data from third parties. In our work, we suggest an approach that allows other processes to read memory of a trusted process, but denies to modify it. Such assumption is useful for cases when trusted application needs to pass some data to other processes by means, for example, of shared memory. That is, our approach protects execution process of a trusted application, but does not hide its whole data from other programs. But if necessary, our system can be easily modified to completely deny access to application's memory.

An advantage of Overshadow is that no modifications are required in existing software (OS, applications) and hardware. More precisely, there are no hardware-specific requirements only if hypervisor used is able to perform virtualization without hardware assistance. However, in this case protection system architecture is bounded to architecture of particular hypervisor. Moreover, such hypervisors for x86 platform are rather complex and they are rather hard to implement (since x86 architecture by itself is hard to virtualize due to design). Among effective implementations, we can mention only VMware VMM (used in Overshadow) and VirtualBox [11]. Since such hypervisors are complex (and in addition, VMware hypervisors are mostly closed source products), it is not easy to modify them to implement additional functionality.

On the other hand, in the last several years Intel and AMD have added virtualization support to their processors and made it easier to create virtualization products [12]. These possibilities are now utilized by such products as Kernel-based Virtual Machine (KVM), Xen, VMware ESX and others. In our approach we assume that target system provide hardware-assisted virtualization. This puts some limitations on hardware where our approach is applicable, but significantly simplifies its implementation.

#### III. CONTROLLING CONSISTENCY OF A TRUSTED PROCESS

In our threat model, we suppose that the operating system is not reliable and contains vulnerabilities which can be exploited by malware to gain high privileges. Such privileges would allow attacker to control all processes running in the system and perform malware injections in their files or directly in the process code in the memory. In our protection system, potentially compromised OS is located inside virtual machine controlled by hypervisor, which is a core part of the protection system. Hypervisor has higher privileges than OS inside VM and can monitor and control events inside VM.

In order to guarantee consistency of a trusted application, hypervisor should guarantee the following:

- application files on disk (in particular, executables and libraries) are not modified by malicious software; in this paper, we only consider executable files and libraries that form the application, ignoring the task of protection of other files and resources that can be used by application (e.g., protection of different data files);

- address space of a running process is not modified in an unallowed way by other processes running in OS.

Let us consider how these tasks are solved by suggested protection system.

#### A. Checking Consistency of Executable Files and Libraries

When launching a trusted application, we should first ensure that executable being launched is an expected one. In order to do this, we should check that application executable file (and shared libraries, if any) on disk was not modified by malicious code. To make such check possible, every trusted application in our system should provide hypervisor with a *registration data*, generated inside trusted environment on the basis of application files. This registration data is stored in hypervisor and cannot be accessed by OS.

Registration data for application executable files and shared libraries consists of SHA-1 hash codes. Such codes are generated for every memory page containing either instructions or static data. Currently we assume that the page size is equal to 4 kilobytes (a default value on most systems). However, nowadays Linux provides support for larger pages [13], and we plan to support such pages in future, as well.

#### B. Protecting Control Flow

In our system, the working virtual machine is provided with a single-core virtual CPU, so OS inside this VM can only use a pure time-sharing multitasking. There is no way to run different processes on different CPU cores in parallel. In particular, at any moment of time either CPU and other resources are used by trusted code or they are used by potentially malicious software. Thus, if we want to protect trusted process, we should only ensure that the process address space and other system resources that can influence process execution (e.g., different system registers) were not modified in a forbidden way while the trusted process was inactive. When trusted process is active, all events in the system are allowed. In particular, trusted process can modify its own code segments in memory. Besides application code and static data loaded at launch, we can control consistency of any data pages loaded by during process execution. More particular, we track states of all memory pages written by the process.

In order to implement such protection, we use hypervisor to handle interruptions of trusted code execution. When a trusted process is interrupted, hypervisor saves information about its address space and other protected resources inside its own memory. Only after that, control is passed to operating system. When OS returns control to the trusted process, hypervisor compares actual state of protected resources with the saved one. If any discrepancy is detected, the protection system reports an attack attempt and the process is not considered to be trusted any more. From that moment, it will not be allowed to use protected system resources (e.g., network connection).

One of the main components of the protection system is a *register integrity checker* used to protect control flow of trusted processes. The control flow is considered to be integral, if the following requirements are met:

- 1) actual address of program entry point is equal to the value specified in the registration data;

- 2) every time the control is passed from the OS kernel to the trusted process, address of instruction invoked in the process is either equal to the instruction where the process was previously interrupted, or is equal to a special signal handler (registered by the process in advance).

The first requirement is checked only when the process is launched using a system call like exec(). More generally, it should be checked when the process enters the trusted mode, but in our work we do not consider situations when the process can enter the trusted mode after the launch. The second requirement is checked every time the control is passed to the trusted process. When such an event occurs, the hypervisor verifies instruction address, as well as values of general purpose, segment and different system registers.

#### C. Protecting Address Space

Hypervisor controls integrity of all virtual memory pages (containing either code or data) of the process. When a trusted process accesses a memory page for the first time, this page is marked as *active*. If the page accessed for the first time contains program code or static data, then it is checked that the page hash sum corresponds to the one specified in the registration data. This allows to verify that the program code and static data were not modified after registration data was generated. Other pages are allowed to have random data when they are accessed by trusted process for the first time. If in the sequel trusted process accesses such a page, the hypervisor checks that the page content was not modified since the last time when it was accessed by the process.

In order to perform such integrity monitoring, hypervisor uses a special control table of process active virtual pages which we call *Memory Integrity Table* (MIT). For every virtual page V, the MIT table contains either address of corresponding physical page P (if V is mapped to a physical memory) or hash sum H if the page is not mapped.

At runtime, programs can detach memory pages from their address space (e.g., by means of munmap() system call). Hypervisor tracks such system calls and removes the *active* mark from the detached pages.

Pages storing dynamic data inside address space of a trusted process can be subjected to legal modifications by the process itself, as well as by some system calls (e.g., read()). If an active page of a trusted process is mapped to a physical page, then write access to that page is allowed for the trusted process only. When a trusted process tries to access a page for which a hash sum is set in the MIT table, hypervisor checks integrity of that page by calculating hash code for its current content and comparing it with the expected value stored in the control table.

Moreover, hypervisor allows only modifications that touch memory areas explicitly specified in the system call parameters. Modifications outside such explicitly specified areas are prohibited. It is important to note that on Intel x86 architecture it is possible to set access permissions on the page-level basis, while processes may want to write data which is not aligned to page size. In order to support protection of such data, hypervisor used special trick based on the fact that for every process one can specified address area writable for kernel with per-byte precision.

Before transferring system call to OS kernel, the protection system for every out parameter allocates a "shadow" memory area inside virtual address space of the process and set registers controlling passing of return values to point to that area. Thus, output of every system call is redirected to memory area not used by the process. When system call returns control to the process, hypervisor copies its output to corresponding areas inside process memory.

In order to maintain mappings in the MIT table and to intercept page access attempts, hypervisor runs every trusted process in a separate *protection domain*. Protection domain is a set of memory pages with individual access permissions. This set of pages for a particular protection domain is dynamically altered by hypervisor when process requests more memory or frees unnecessary pages. Every attempt to access a page outside the protection domain, as well as access violation for the page inside the domain, leads to exception which is caught and handled by hypervisor.

Implementation of protection domains is based on the Nested Page Tables (NPT) mechanism (NPT implementation in Intel processors is called *Extended Page Tables*, the one from AMD - Rapid Virtualization Indexing). NPT tables are used to perform translation of pseudo-physical addresses used inside VM to physical addresses of the real hardware. When a process is launched in the trusted mode, hypervisor creates an empty set of NPT tables for it. Every time when OS kernel passes control to the trusted process, hypervisor activates page tables corresponding to that process. This is performed by means of the Virtual Machine Control Block (VMCB) structure. When trusted process is interrupted and control is passed back to the OS kernel, hypervisor switches active nested pages once again and activates tables of untrusted domain (a joint domain for OS kernel and other untrusted processes).

When a process tries to access a page which is not yet reflected in the NPT tables, or when access violation occurs, a Nested Page Fault (#NPF) exception is thrown, VM is stopped and control is passed to the hypervisor. Hypervisor maintains NPT mapping only for active pages which are not swapped out to the storage device and which were not modified by third-party processes. This approach allows to determine if the process accesses a page for the first time or it accesses pages which were modified since the last access by this process or loaded from swap.

When the #NPF exception is thrown, a pseudo-physical address of page inside VM is reported, access to which led to the exception. However, in order to get the expected hash sum for the page from the control tables, hypervisor should also know a virtual address, access to which finally led to #NPF. In order to calculate virtual address, hypervisor disassembles the current instruction of the trusted process (address of such instruction is always stored in the IP register) and analyzes all virtual addresses accessed by this instruction. Using page table of the operating system, hypervisor calculates real addresses corresponding to these virtual ones and detects which of them corresponds to the pseudo-physical address access to which led to the #NPF exception. With this virtual address, the hypervisor is able to verify integrity of the page accessed by the trusted process.

#### D. Protecting Dynamically Linked Applications

Address space protection approach described above easily applies for statically linked programs. Such a program is represented by a single executable file that does not import any libraries from the OS, so we can know in advance location of code and static data inside the application. However, nowadays developers often take an advantage of using splitting functionality between separate libraries which are combined together by the loader during program start up or even loaded by request during program execution (such functionality is provided in Linux by **libdl** library). Protection of such programs (especially those that use libdl functionality) introduces new challenges.

Dynamically linked application consists of a main executable file and several libraries loaded by dynamic loader during application launch. In Linux, for both executable files and dynamic libraries ELF format is used. Every ELF file has a set of DT\_NEEDED entries which store names of libraries that should be loaded with this file. When launching an executable, dynamic loader processes DT\_NEEDED entries of the file itself, then DT\_NEEDED entries of libraries loaded as file dependencies and so on – such iterations are performed until DT\_NEEDED entries of all files from the loaded set are satisfied by files from this set.

The set of DT\_NEEDED entries can be extracted from the ELF file by means of appropriate tools. However, the final set of loaded libraries can be different for the same executable in different Linux distributions, because internal dependencies of libraries can differ. Moreover, in addition to dependencies statically recorded in the ELF file structures which are resolved during file launch, it is possible to load libraries at runtime by means of functions provided by libdl library. In many cases,

it is almost impossible to automatically detect which libraries will be loaded using such functionality, because the name of the library to be loaded can be calculated at runtime.

Due to these facts, in our approach user should explicitly list all the libraries that will be loaded during application work in particular system. This set considered to be a set of trusted files. If a library not included in this set will be loaded and put to the application address space, this will be reported as an attack attempt.

In addition to libraries, for every dynamically linked application the Linux kernel exposes a shared object called *Virtual Dynamically-linked Shared Object* (VDSO) which exports symbols implementing virtual system calls [14]. Traditionally, system calls in Linux on the x86 platform were implemented using 0x80 software interrupt. With modern processors, faster implementations are available that use SYSCALL or SY-SENTER instructions for AMD and Intel processors respectively. For every of these techniques, the Linux kernel has a corresponding VDSO variant. Implementation of all these three VDSO variants can be extracted from the Linux kernel sources.

Thus, a memory image of a dynamically linked application consists of the following components:

- executable file (launched by user or by other process);

- dynamic loader (usually ld-linux.so);

- set of libraries specified as ELF file dependencies and loaded at application start;

- set of libraries loaded at runtime using libdl functionality;

- VDSO library.

Registration data of dynamically linked application should contain information about all these components.

An important feature of dynamic libraries is that their code is position-independent and can be located any area of application's address space. Address value specified in the ELF file header in Linux running on x86 platform nowadays is just a recommendation for the loader. In reality, dynamic loader can place every file at other address, and such addresses can vary in different systems or even in different instances of the same application.

Note that since VDSO is a shared object, it can also be located at any address inside process address space. Thus, location of VDSO in process memory can be different for different processes.

Finally, executable files can also contain positionindependent code. Executable files that consist of such code only (*Position-Independent Executables*, PIE) are relatively widespread in the Linux ecosystem.

Thus, every component of dynamically linked application can be located at any virtual address inside application address space. Since the memory is allocated and managed on the per-page basis, correlation between actual address of every component and the value specified in ELF header is expressed by the following formula:

$Actual\_address = ELF\_address + k * (page\_size)$

where k is some integer number.

Thus, though location of different components of dynamically linked application in virtual memory is not known in advance, these locations can be easily calculated by hypervisor during application start up. Location of libraries loaded using libdl functions can be calculated at the moment when dlopen()function is invoked. This allows to adopt registration data for every particular launch of application. As we will discuss later, the only thing hypervisor has to calculate is a difference between real address and the value specified in the ELF header (and thus reflected in the registration data) which is identified by a single integer number k. It is important to note that since library code is position independent, it is not subjected to any modifications by loader.

Before passing control to entry point of dynamically linked application, dynamic loader should link together all components of application and set actual addresses of all imported symbols. For the context protection system, it is important to ensure that no malicious code interfere with this process, replacing address of legal imported function with address of malicious symbol. Let us proceed with details of dynamic loader work process and see how protection system guarantees consistency of function addresses.

During dynamic linking process, system loader first loads all necessary files to memory and then initiates symbol resolution process. For every binary symbol imported by some ELF file (this file is called *importer*) the loader should locate the file where the symbol is implemented (this file is called *exporter*). Dynamic loader analyzes symbol tables of exporter and importer and updates the Global Offset Table (GOT), which is located at the data segment of the importer. The GOT table contains an entry for every imported binary symbol (corresponding to a function o global variable). Symbol resolution procedure is the same for libraries loaded during application launch and the one loaded at runtime using libdl functionality.

Code segment of ELF file that imports some functions contains Procedure Linkage Table (PLT) which contains a *stub* symbol for every imported function. When an attempt is performed to call some imported function, the control is passed to the corresponding stub which takes unnecessary address from the GOT table and passes control to that address. Thus, a call to an imported function is an indirect call by address recorded in the appropriate GOT table entry.

GOT and PLT tables used when a call to imported function happens are located in the segments of that ELF file from which the call is performed. Thus, they are taken into account when file hash sum is calculated and monitored by the protection system during application work. The whole dynamic linking process, including modification of the GOT table, is performed by the dynamic loader which works in the user space. The process requires no kernel-level activities and thus cannot influence other applications in case of errors. This is one of the advantages of using ELF format for executable files.

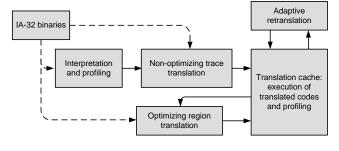

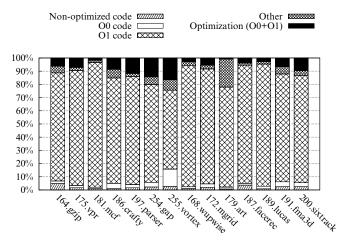

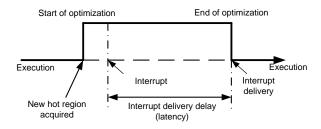

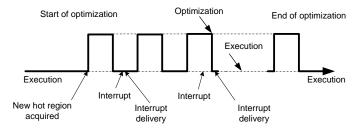

Thus, if dynamic loader is a trusted program, then all the actions during dynamic linking are performed by trusted code. Dynamic loader is much more smaller then the Linux kernel and it does not vary significantly among different distributions (in particular, it does not allow insertion of some third-party software such as drivers in its code). Thus, we believe that it is reasonable to consider dynamic loader to be a trusted process. In the rest of the paper, we use the assumption that the dynamic loader is a trusted program. Note that since dynamic loader is included in the process image, hypervisor is able to compare its content with registration data. Thus, the protection system is able to check that the loader is the same as the one in the system where the registration data was generated.